# **KNJN FX2 FPGA development boards**

© 2005 - 2024 KNJN LLC

https://www.knjn.com/

This document applies to the following boards.

- Saxo-L (revisions B & above)

- Saxo-Q

- Xylo (revision E)

- Xylo-E (revisions B & above)

- Xylo-EM

- Xylo-L

- Xylo-LM

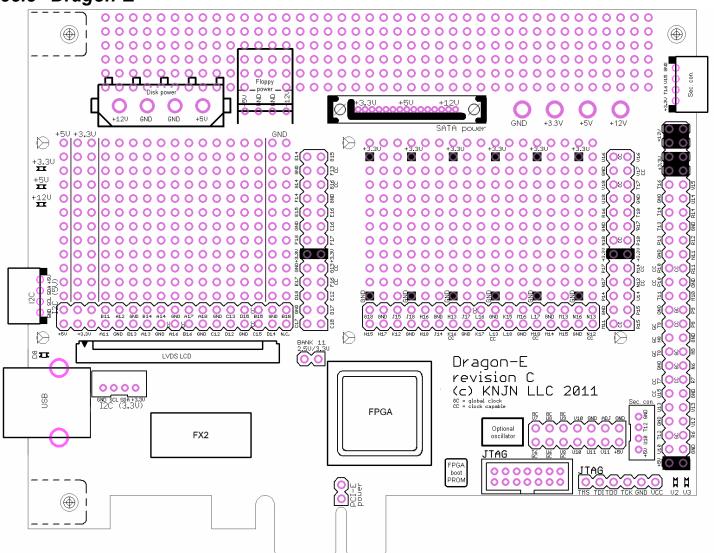

- Dragon-E (revision B & above)

Last revision March 30, 2024

# **Table of Contents**

| 1 Welcome                                                      | 6  |

|----------------------------------------------------------------|----|

| 1.1 This guide                                                 |    |

| 1.2 FPGAs the easy way                                         |    |

| 1.3 ARM processor                                              |    |

| 1.4 Windows and other OSes                                     | 6  |

|                                                                |    |

| 2 Boards features                                              | /  |

|                                                                |    |

| 2.2 Block diagram and features checklist                       |    |

| 3 Software tools                                               |    |

| 3.1 Important downloads                                        |    |

| 3.2 FPGA software                                              |    |

| 3.3 C/C++ compiler                                             |    |

| 4 Board installation                                           |    |

| 4.1 USB driver installation                                    |    |

| 4.2 Windows device manager                                     |    |

| 5 FPGA configuration                                           |    |

| 6 FPGA boot-PROM                                               | 12 |

| 6.1 FPGA at power up                                           |    |

| 6.2 Boot-PROM and USB                                          |    |

| 6.3 Boot-PROM and JTAG                                         | 12 |

| 7 Advanced FPGA control                                        | 13 |

| 7.1 More FPGA actions                                          | 13 |

| 7.2 Auto-mode                                                  |    |

| 7.3 Options                                                    |    |

| 7.4 Log                                                        |    |

| 8 Your own FPGA project                                        |    |

| 8.1 LEDblink.                                                  |    |

| 8.2 The FPGA doesn't configure?                                |    |

| 8.3 The boot-PROM fails to configure the FPGA?                 |    |

| 9 FPGA projects with Altera's Quartus (Saxo-L/-Q and Xylo/-EM) | 15 |

| 10 FPGA projects with Xilinx's ISE (Xylo-L/-LM and Dragon-E)   | 15 |

|                                                                |    |

| 11 FPGA pins                                                   |    |

| 11.1 Common pin assignments                                    |    |

| 11.2 Clocks                                                    |    |

| 11.3 LEDs                                                      |    |

| 11.4 Push-button                                               |    |

| 11.5 VGA (Xylo/-EM only)                                       |    |

| 11.6 Secondary connector                                       | 18 |

| 11.7 Text LCD (Saxo-L & Xylo/-E only)                          |    |

| 11.8 I2C (all boards)                                          |    |

| 11.9 Ethernet signals (Xylo/-E/-EM/-L/-LM only)                | 18 |

| 11.10 HDMI (Xylo-E only)                                       | 18 |

| 11.11 SD card (Xylo-E only)                                    | 18 |

| 12 USB/FX2 interface                                           | 19 |

| 12.1 Bulk vs. Isochronous                                      | 19 |

| 12.2 FX2 interface and FIFOs                                   | 19 |

| 12.3 PC to FPGA                                                | 19 |

| 12.4 FPGA to PC                                                |    |

| 12.5 FIFO flags                                                |    |

| 12.6 FIFO data, address and control lines                      |    |

| 12.7 FIFO signal names                                         |    |

| 13 PC access to the FX2 FIFOs.                                 |    |

| 13.1 FIFO access with the CyUSB driver.                        |    |

| 13.2 FIFO access with the EzUSB driver                         |    |

| 13.2 FIFO access with the E2036 driver                         |    |

|                                                                |    |

| 14.1 Example 1: LED control                                    |    |

| 14.2 Example 2: Text LCD                                       |    |

| 14.3 Example 3: Bidirectional communication                    |    |

| 14.4 Example 4: SDRAM (Xylo-EM/LM only)                        |    |

| 14.5 Example 5: DDS (Saxo-Q only)                              |    |

| 15 Ethernet (Xylo-E/-EM/-L/-LM only)                           | 25 |

|     | 15.1 Ethernet board setup                             |      |

|-----|-------------------------------------------------------|------|

|     | 15.2 Ethernet HDL reference design                    | 25   |

|     | 15.3 Troubleshooting – the PC has troubles receiving  | 25   |

|     | 15.4 Troubleshooting – the PC has troubles sending    | 25   |

|     | 15.5 UDP tester                                       | 25   |

| 16  | 12C bus                                               | . 26 |

|     | 16.1 I2C controller                                   | 26   |

|     | 16.2 On board devices                                 | 26   |

|     | 16.3 Bus scan                                         |      |

|     | 16.4 Write & Read                                     |      |

|     | 16.5 Custom commands                                  |      |

|     | 16.6 PLLs                                             |      |

|     | 16.7 EEPROM                                           |      |

| 17  | I2C EEPROM                                            |      |

| • • | 17.1 EEPROM purposes.                                 |      |

|     | 17.2 EEPROM adapter board                             |      |

| 18  | USB IDs                                               |      |

| 10  | 18.1 Custom IDs.                                      |      |

|     | 18.2 Default IDs.                                     |      |

|     | 18.3 hex2bix                                          |      |

|     | 18.4 USB-IF                                           |      |

|     | 18.5 Checking the USB ID of a plugged board           |      |

| 10  | 80518051                                              |      |

| 19  |                                                       |      |

|     | 19.1 8051 processor                                   |      |

|     | 19.2 8051 programming                                 |      |

|     | 19.3 HEX files                                        |      |

|     | 19.4 Power-up                                         |      |

| 20  | I2C-over-USB protocol                                 |      |

|     | 20.1 Background                                       |      |

|     | 20.2 Protocol                                         |      |

|     | 20.3 Command packet                                   |      |

|     | 20.4 Response packet                                  |      |

|     | 20.5 Restrictions.                                    |      |

|     | 20.6 I2C start/restart/stop                           |      |

|     | JTAG FPGA configuration                               |      |

|     | 21.1 Configuration files                              | 34   |

|     | 21.2 JTAG FPGA configuration with Altera's Quartus-II | 34   |

|     | 21.3 JTAG FPGA configuration with Xilinx's ISE        |      |

| 22  | JTAG FPGA support in Altera's Quartus-II              |      |

|     | 22.1 JTAG                                             |      |

|     | 22.2 JTAG connection                                  | 35   |

|     | 22.3 JTAG connector                                   |      |

| 23  | JTAG-over-USB for Altera FPGAs                        | 36   |

|     | 23.1 Protocol emulation                               | 36   |

|     | 23.2 Board support                                    |      |

|     | 23.3 Non pre-wired boards                             |      |

|     | 23.4 Switch to JTAG-over-USB mode                     |      |

|     | JTAG boot-PROM programming with Altera's Quartus-II   |      |

| _ : | 24.1 Create the JTAG Indirect Configuration File      |      |

|     | 24.2 Program the boot-PROM                            |      |

|     | Graphic LCD.                                          |      |

| 20  | 25.1 KNJN graphic LCDs (all boards)                   |      |

|     | 25.2 LVDS LCD panel (Dragon-E only)                   |      |

|     | 25.3 Other graphic LCDs                               |      |

|     | Flashy                                                |      |

| 20  | 26.1 What is Flashy                                   |      |

|     |                                                       |      |

| 27  | 26.2 Flashy connection                                |      |

|     | Flashy designs                                        |      |

|     | 27.1 FlashyMini                                       |      |

|     | 27.2 FlashyDemo                                       |      |

|     | 27.3 Flashy vs. Widy                                  |      |

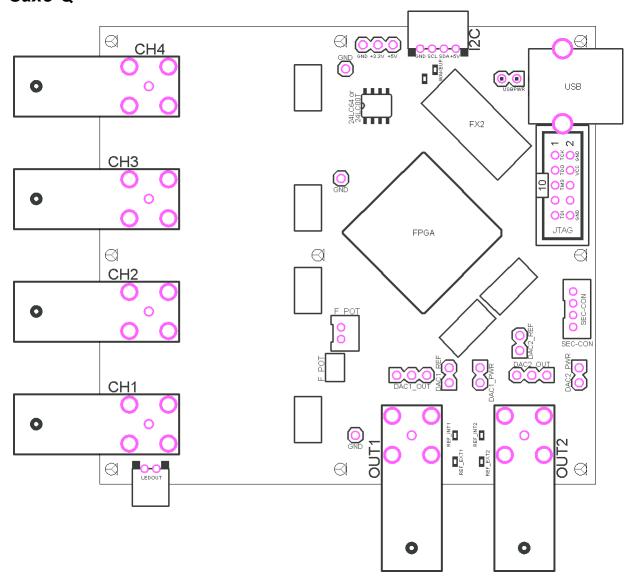

| 28  | Saxo-Q                                                | . 41 |

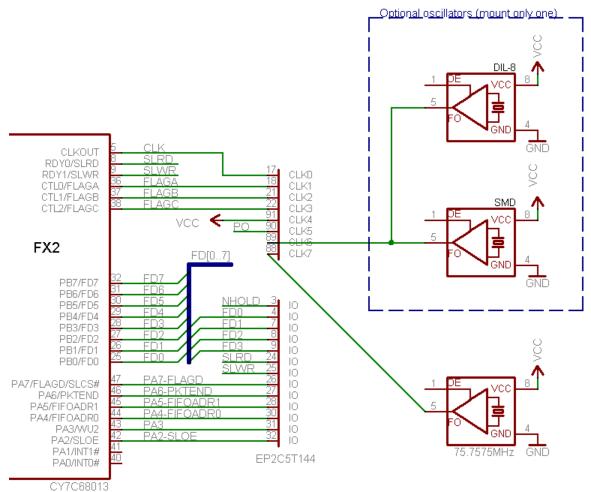

| 28.1 FX2 and clock c     | connections                          | 41 |

|--------------------------|--------------------------------------|----|

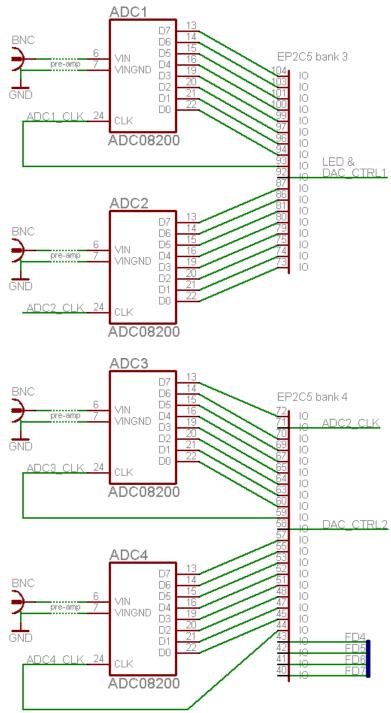

| 28.2 ADC inputs          |                                      | 42 |

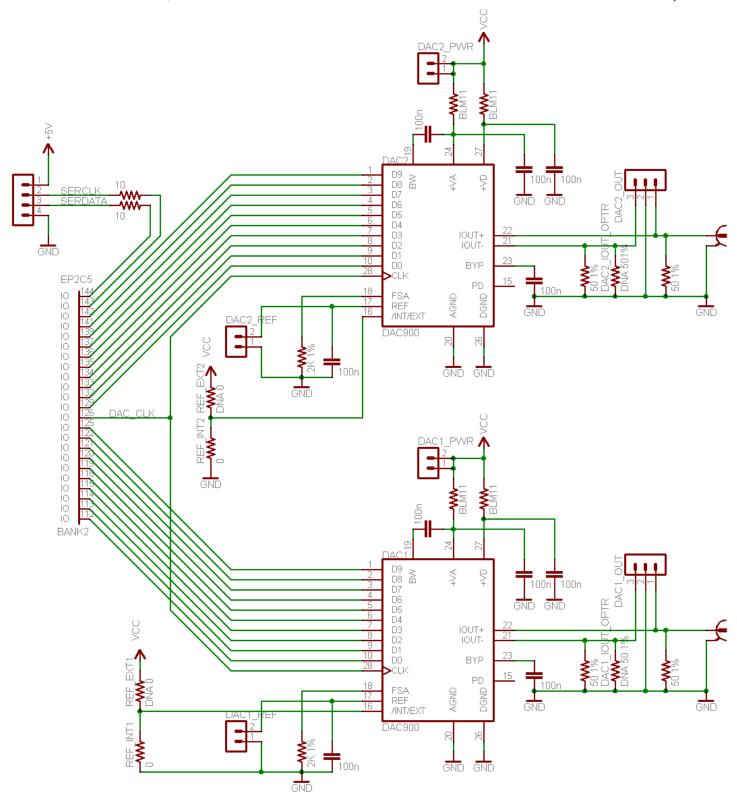

| 28.3 DAC outputs         |                                      | 43 |

|                          |                                      |    |

| 29.1 RS-232 with the     | e FPGA                               | 44 |

| 29.2 Serial interfaces   | s with the ARM (Saxo-L & Xylo-L/-LM) | 44 |

| 30 Text LCD              |                                      | 45 |

| 30.1 Text LCD conne      | ector (Saxo-L & Xylo)                | 45 |

| 30.2 Manual wiring (>    | Xylo-L/-LM/-EM)                      | 45 |

|                          | nple                                 |    |

| 31 Board power (all boar | rds but Dragon-E)                    | 46 |

| 31.1 USB power           |                                      | 46 |

|                          |                                      |    |

| 31.3 External power      |                                      | 46 |

| 31.4 Current measure     | ement                                | 46 |

| 32 Board power (Dragon   | n-E only)                            | 47 |

| 32.1 Power rails         |                                      | 47 |

| 32.2 Power sources       |                                      | 47 |

| 32.3 Possible board ι    | uses                                 | 47 |

|                          |                                      |    |

|                          |                                      |    |

| 33.2 EzUSB (32bit W      | Vindows only)                        | 48 |

| 33.3 CyUSB (32bit ar     | nd 64bit Windows)                    | 48 |

|                          | ignature                             |    |

|                          | and GUID                             |    |

| 33.6 Multiple instance   | es                                   | 48 |

|                          | river                                |    |

| 34.1 USB port            |                                      | 49 |

|                          | ng the Windows Device Manager        |    |

|                          | ng devcon                            |    |

| 34.4 Removing a driv     | ver from DriverStore repository      | 49 |

| 35 Other OSes support    |                                      | 50 |

|                          |                                      |    |

|                          | ators                                |    |

|                          | X2 firmware                          |    |

|                          | & receive sample C code              |    |

|                          | e C code                             |    |

|                          | n assignments                        |    |

|                          |                                      |    |

|                          |                                      |    |

|                          |                                      |    |

|                          |                                      |    |

| •                        |                                      |    |

| •                        |                                      |    |

|                          |                                      |    |

|                          |                                      |    |

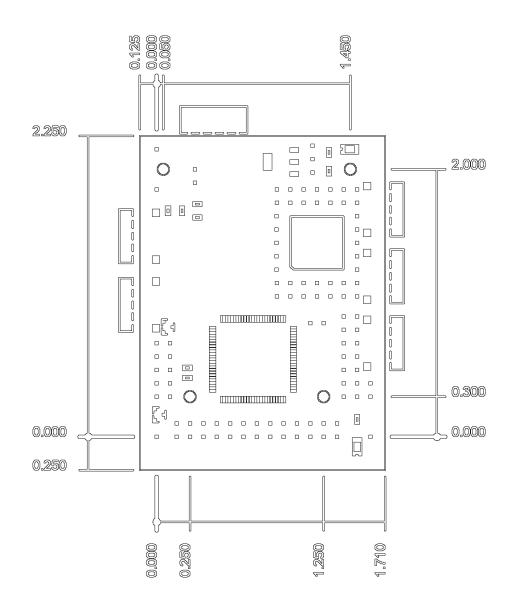

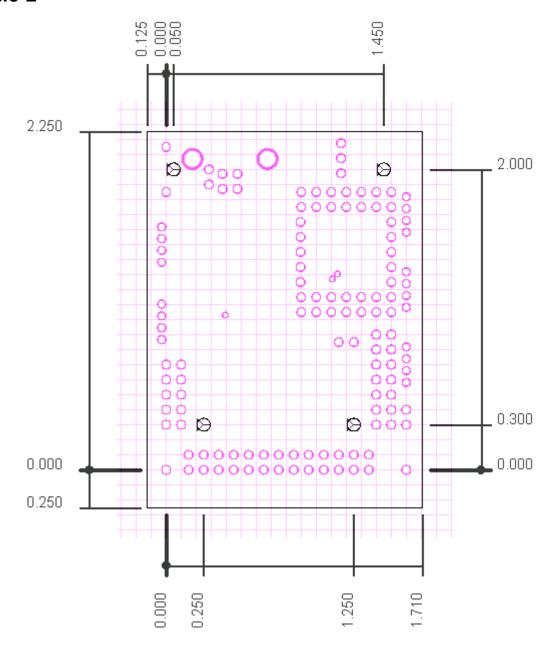

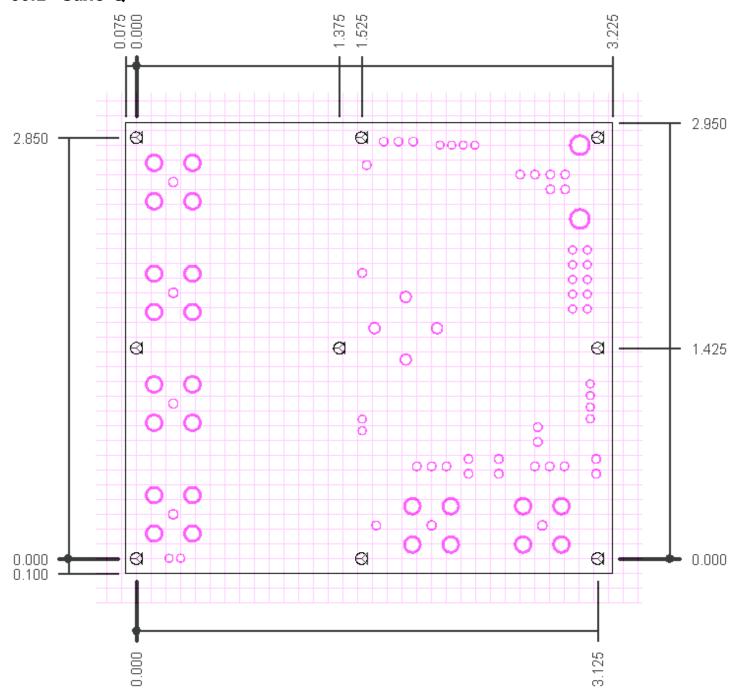

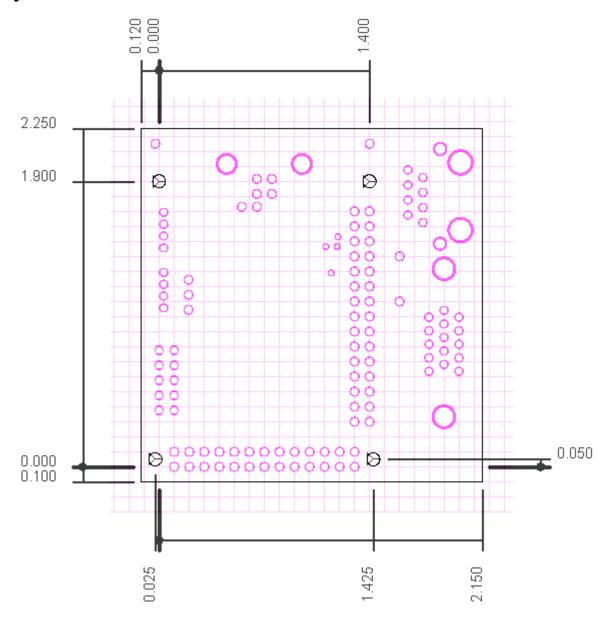

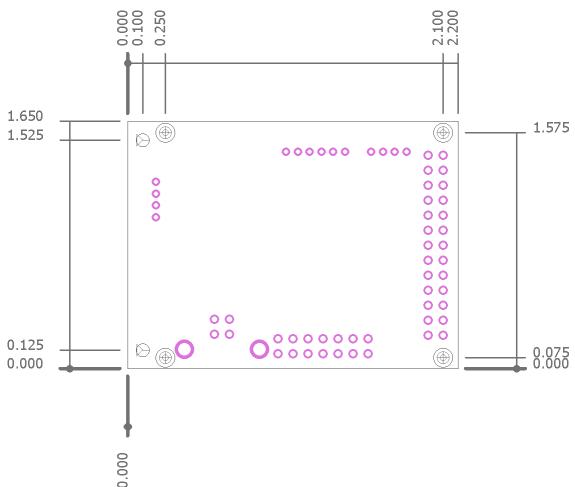

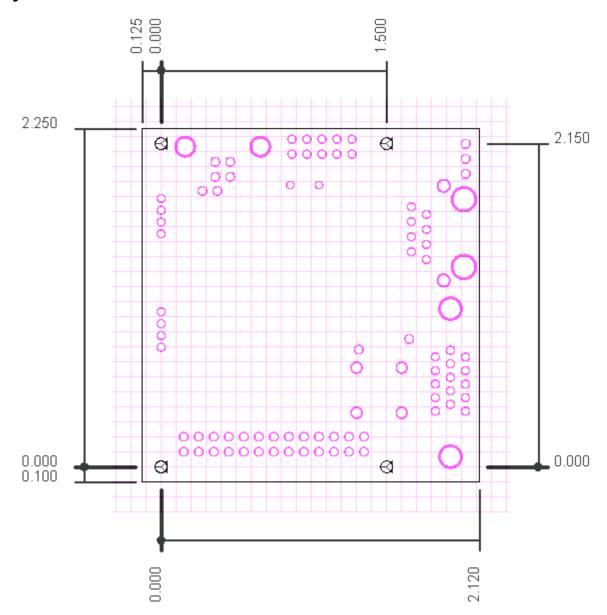

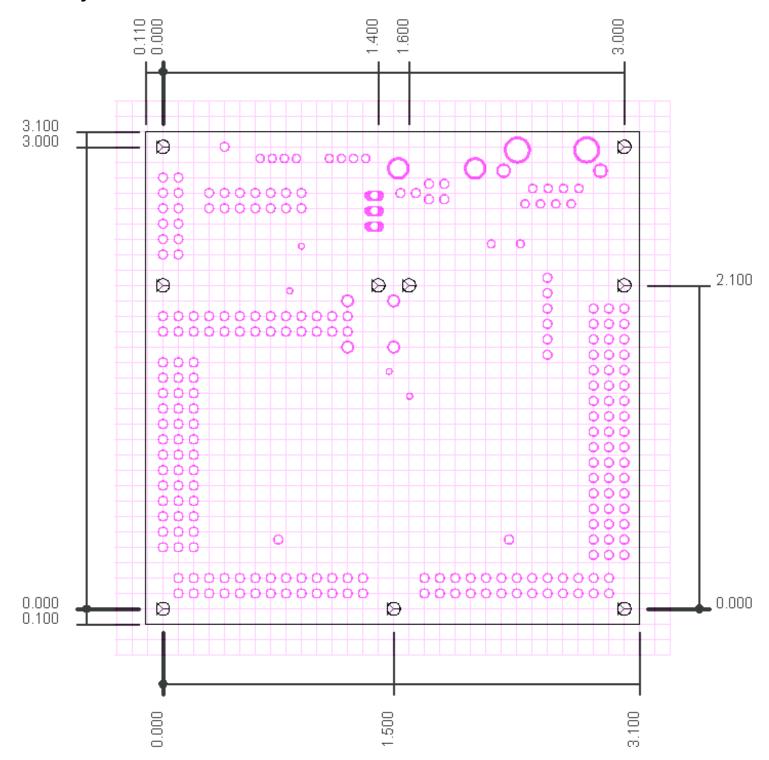

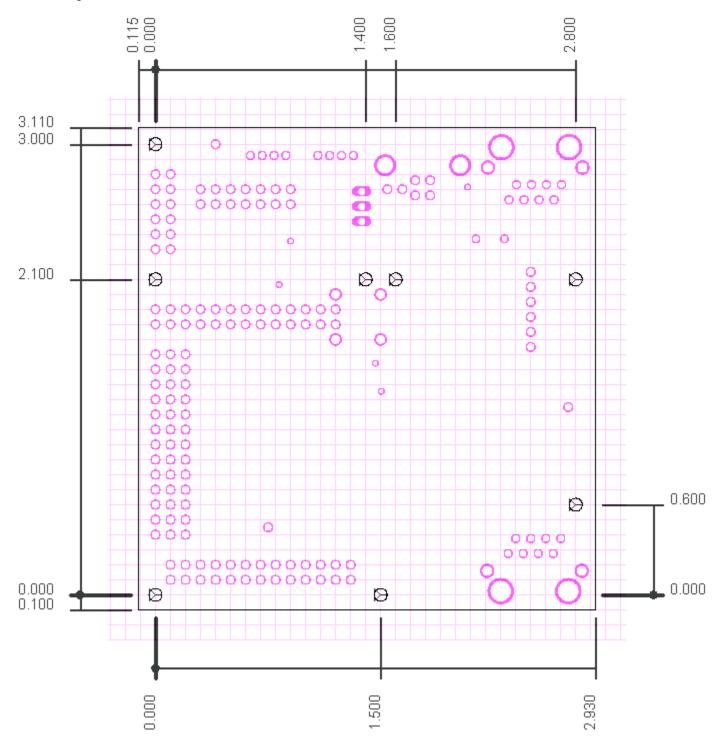

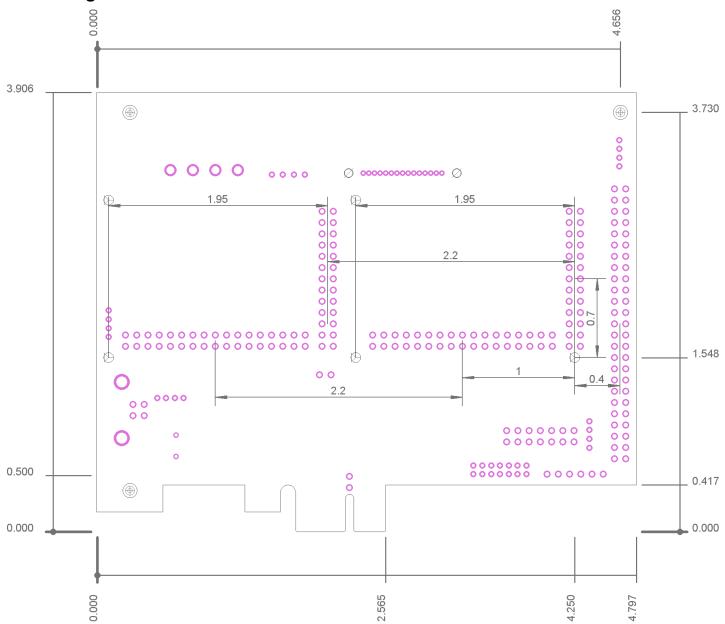

| 39 Mechanical drawings   | S                                    | 61 |

|                          |                                      |    |

|                          |                                      |    |

|                          |                                      |    |

|                          |                                      |    |

| -                        |                                      |    |

| •                        |                                      |    |

|                          |                                      |    |

| <u> </u>                 |                                      |    |

| 40 Errata                |                                      | 69 |

## 1 Welcome

### 1.1 This guide

Welcome to the KNJN FX2 FPGA development board guide. It is partitioned in short and easy to read chapters, and explains how to work with your new FPGA board.

## 1.2 FPGAs the easy way

Although FPGA boards can be intimidating, KNJN FPGA boards are easy to use. KNJN FX2 boards work right out of the box with a simple USB connection, so that you can get up to speed quickly and concentrate on your task.

For example, one of the first tasks this document walks you through is the FPGA configuration. Basically you plug your board into one of your Windows PC's USB ports, go through the Windows wizard to install a provided USB driver, open the FPGA configuration software, select one of the provided bitfiles and click on the "Configure!" button.

Voila! You've configured the FPGA within just a few minutes.

That's only the beginning. Through this document, you will see how easy it is to program the FPGA boot-PROM, speak to I2C peripherals, transform your board into a digital oscilloscope, transfer data from the FPGA to the PC, drive an LCD...

Welcome to the FPGA world.

### 1.3 ARM processor

If your board has an ARM processor, you also need the "KNJN FX2 ARM boards" guide. The KNJN guides are available from <a href="http://www.knjn.com/docs/">http://www.knjn.com/docs/</a>

#### 1.4 Windows and other OSes

The KNJN boards are supported on the latest versions of Windows (7 / 8 / 8.1 / 10 / 11). They can also be used in JTAG mode with other OSes like Linux and Mac OS (chapter 35).

# 2 Boards features

# 2.1 The KNJN FX2 FPGA family of boards

The FX2 FPGA boards are based on Xilinx and Altera FPGAs, plus LPC213x ARM processors.

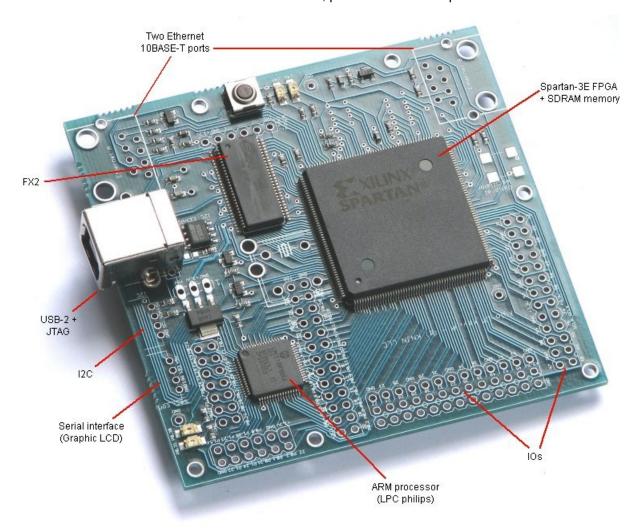

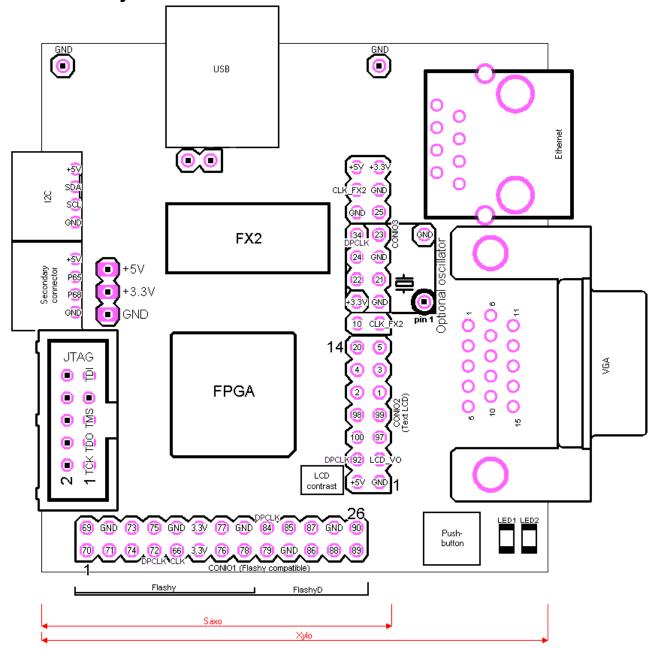

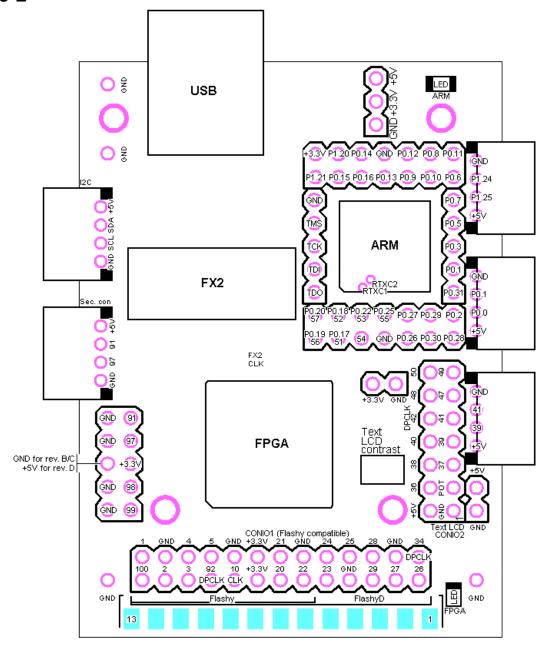

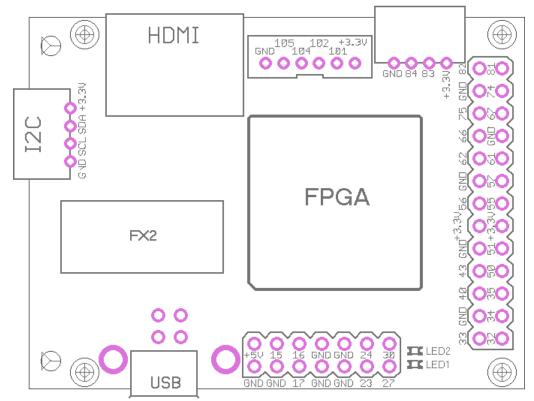

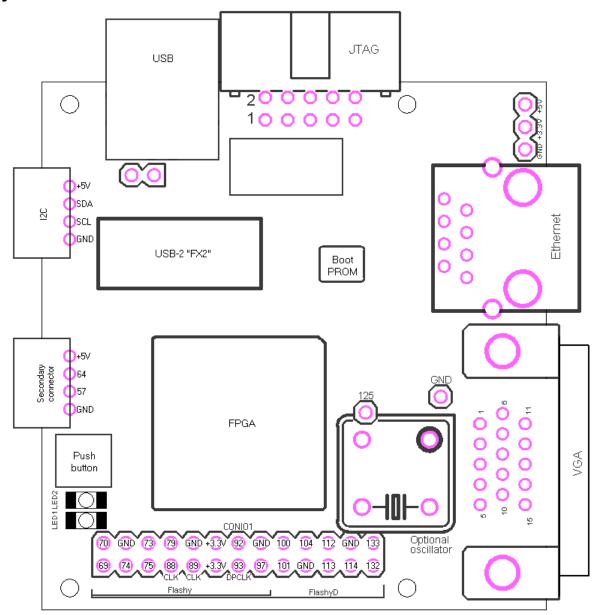

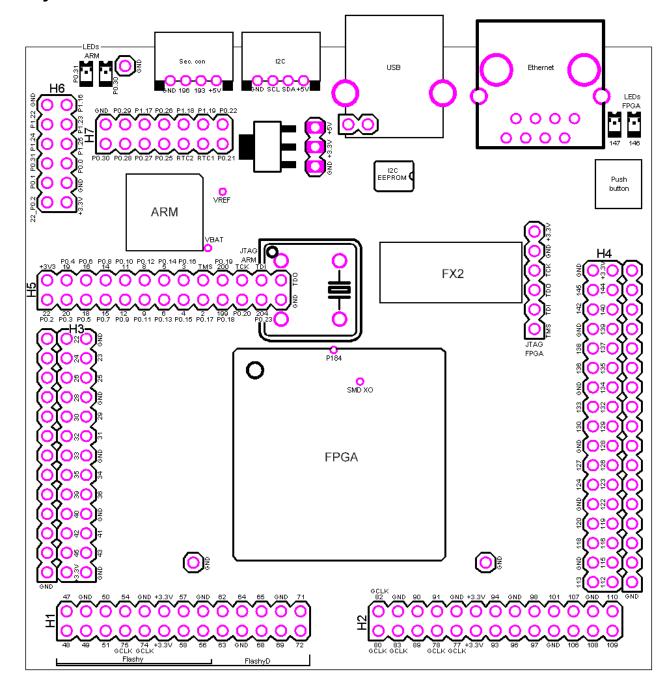

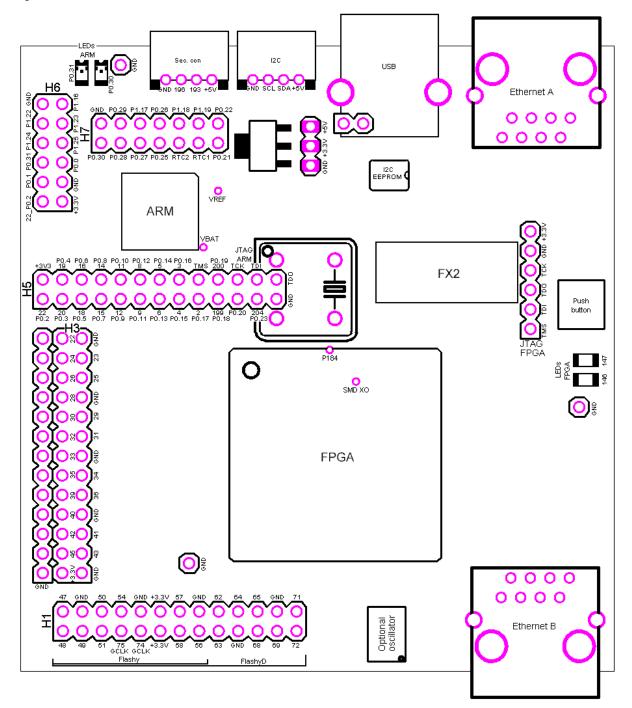

"Xylo-LM", member of the KNJN FX2 family of boards.

Like all KNJN FPGA boards, the FX2 boards features an easy to use link to a PC. Here, that's a high-speed USB-2 port, which allows typical PC  $\leftrightarrow$  FPGA communication speeds of 30MB/s to 40MB/s (240Mbit/s to 320Mbit/s).

The FX2 FPGA family of boards currently has eight members. Each member has unique features, the latest ones are:

- Xylo-E with HDMI, SDRAM plus optional SD card and Ethernet.

- Saxo-Q with several high-speed analog channels (ADCs and DACs).

- Dragon-E with a PCI Express interface.

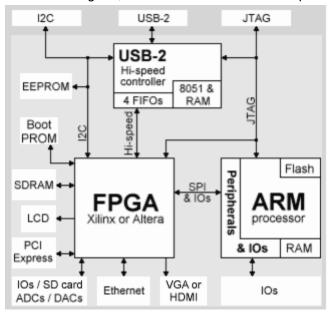

# 2.2 Block diagram and features checklist

Here's the FX2 FPGA family of boards block diagram, check the table below for the particular features of each board.

| Board name           | Saxo-L              | <u>Xylo</u>     | Xylo-E            | Xylo-EM         | Xylo-L              | Xylo-LM             | Saxo-Q             | Dragon-E            |

|----------------------|---------------------|-----------------|-------------------|-----------------|---------------------|---------------------|--------------------|---------------------|

| Main PC interface(s) | USB                 | USB             | USB               | USB             | USB                 | USB                 | USB                | PCI Express & USB   |

| FPGA                 | Altera<br>EP1C3     | Altera<br>EP1C3 | Xilinx<br>XC6SLX9 | Altera<br>EP2C5 | Xilinx<br>XC3S500E  | Xilinx<br>XC3S500E  | Altera<br>EP2C5    | Xilinx<br>XC5VLX20T |

| Datasheet            | Cyclone             | <u>Cyclone</u>  | Spartan-6         | Cyclone II      | Spartan-3E          | Spartan-3E          | Cyclone II         | <u>Virtex-5</u>     |

| Logic cells          | 2910                | 2910            | 9152              | 4608            | 10476               | 10476               | 4608               | 12480               |

| FPGA boot-PROM (1)   | 1Mbit               | 1Mbit           | 4Mbit             | 4Mbit           | 4Mbit               | 4Mbit               | 4Mbit              | 8Mbit               |

| IOs / clocks         | 40 / 4              | 36 / 4          | 32 / 5            | 17 / 3          | 104 / 7             | 58 / 5              | 0/3                | 130 / 13            |

| PLLs / DCMs          | 1/0                 | 1/0             | 2/4               | 2/0             | 4 / 0               | 4 / 0               | 2/0                | 1/2                 |

| ARM processor        | LPC2132/<br>LPC2138 | -               | -                 | -               | LPC2132/<br>LPC2138 | LPC2132/<br>LPC2138 | -                  | -                   |

| SDRAM                | -                   | -               | 16Mbit            | 16Mbit          | -                   | 256Mbit             | -                  | -                   |

| SD card              | -                   | -               | optional          | -               | -                   | -                   | -                  | -                   |

| Ethernet             | -                   | 10BASE-T        | optional          | 10BASE-T        | 10BASE-T            | 10BASE-T x 2        | -                  | -                   |

| I2C master/bus       | yes                 | yes             | yes               | yes             | yes                 | yes                 | yes                | yes                 |

| High-speed USB-2     | yes                 | yes             | yes               | yes             | yes                 | yes                 | yes                | yes                 |

| Text LCD connector   | yes                 | yes             | yes               | -               | -                   | -                   | -                  | yes                 |

| Graphic LCD ready    | yes                 | yes             | yes               | yes             | yes                 | yes                 | yes                | yes (LVDS)          |

| Video connector      | -                   | VGA             | HDMI              | VGA (note 2)    | -                   | -                   | -                  | -                   |

| Analog outputs (DAC) | -                   | -               | -                 | -               | -                   | -                   | 2 x 10-Bit 165MSPS | -                   |

| Analog inputs (ADC)  | - (note 3)          | - (note 3)      | - (note 3)        | - (note 3)      | - (note 3)          | - (note 3)          | 4 x 8-Bit 200MSPS  | - (note 3)          |

| Dimensions           | 44x60mm             | 57x60mm         | 42x56mm           | 57x60mm         | 81x82mm             | 81x77mm             | 84x77.5mm          | 122x89mm (4)        |

<sup>(1)</sup> Minimum boot-PROM size shown here. Actual product may use a higher capacity boot-PROM.

<sup>(2):</sup> Five VGA IOs are shared with the IOs of the main board header.

<sup>(3):</sup> FlashyD ready (two analog inputs). FlashyD is sold separately.

<sup>(4):</sup> Dimensions don't include the PCI Express connector.

# 3 Software tools

## 3.1 Important downloads

Each KNJN FPGA board is provided with a "startup kit" that includes documentation and other files (mainly example source codes). The startup kit doesn't include some important software tools that are required to work with the FPGA board:

- An "FPGA software"

- A C/C++ compiler

### 3.2 FPGA software

An FPGA software will allow you to generate FPGA bitfiles.

Each FPGA vendor provides a software with a complete tool chain (synthesis and P&R), nicely integrated together. The software is available in a free version (which may be all you'll ever need) and a non-free version (with typically more features and support for bigger devices).

Get the software that matches your board.

- For Saxo-L and Xylo, get Quartus II Web Edition 11.0 SP1 (2.7GB)

- For Saxo-Q and Xylo-EM, get Quartus II Web Edition 13.0 SP1 (4.4GB)

- For Xylo-E/-L/-LM & Dragon-E, get <u>ISE WebPACK 14.7</u> (7.8GB).

Note that ISE WebPack 14.7 comes in two versions:

- ISE Design Suite for Windows 10 (virtual machine): Use this on Windows 10 or Windows 11.

- ISE Design Suite (native Win32/64 or Linux): Use this on Windows 10 or Linux.

## 3.3 C/C++ compiler

A C/C++ compiler is optional but you'll need one for many projects.

Here are different C compilers that can be used:

- Microsoft Visual Studio Community

- Digital Mars

- Jacob Navia's <u>lcc-win32</u>

## 4 Board installation

#### 4.1 USB driver installation

Let's plug your board in!

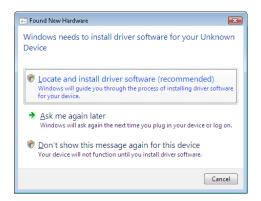

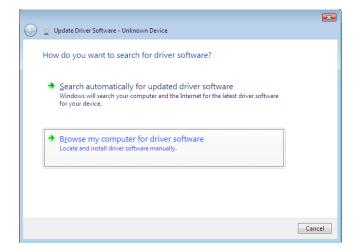

1. Connect your board to one of your PC's USB ports. Windows detects the board and starts its "Hardware Update Wizard".

2. Instruct the wizard to use CyUSB (from the startup kit "USB drivers" directory). If Windows asks about the driver not being Windows-certified, select "continue anyway".

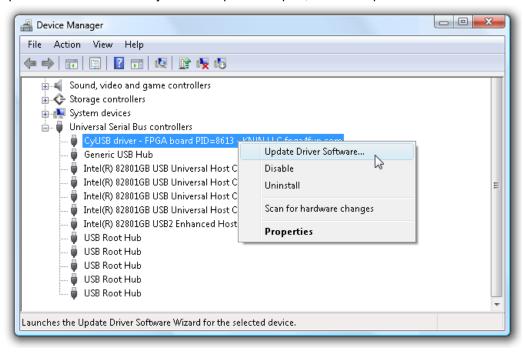

For Windows 7 and above, the wizard may not offer the ability to select the driver directory and then fail... The workaround is simple. Complete the wizard and with the board still connected, open Windows Device Manager, find the board in the USB devices list, and update the driver there.

# 4.2 Windows device manager

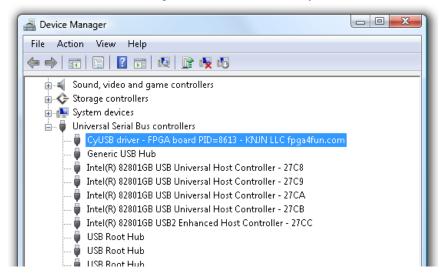

Once the driver is installed, Windows device manager shows the board entry in the USB controllers section.

# 5 FPGA configuration

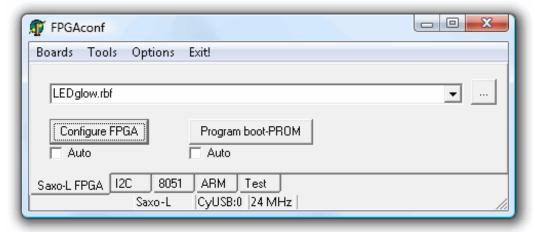

Now that the board is connected and the USB driver installed, let's configure the FPGA.

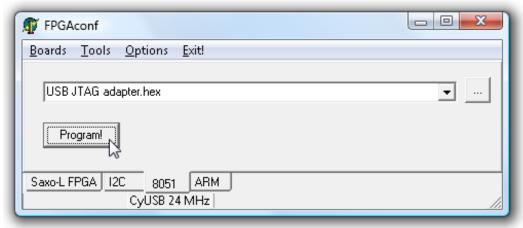

- 1. Run FPGAconf

- 2. Go to menu → Boards and select your FPGA board.

- 3. Go to menu → Options → USB driver and select the USB driver you chose earlier (CyUSB usually). If you are unsure which driver is used, open Windows device manager (see 4.2).

We are ready to configure the FPGA:

- 4. Click on the browse button to select an FPGA bitfile (the browse button is shown as "..."). For your convenience, sample "ledblink" and "ledglow" bitfiles are provided in the startup kit ("FPGA Project LED").

- Click on "Configure FPGA".After a few seconds, the FPGA is configured.

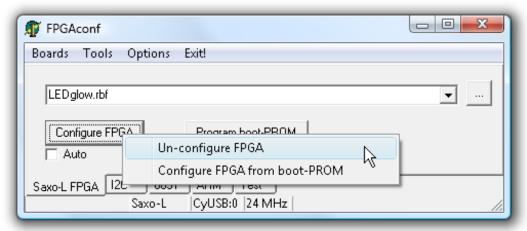

Now **right-click** on the "Configure FPGA" button and select "Un-configure FPGA". You'll notice that when the FPGA is powered but not configured, it is idle and the FPGA LEDs glow slightly. With practice, you'll be able to recognize immediately if the FPGA is configured or not.

## 6 FPGA boot-PROM

Your board has an FPGA boot-PROM. Let's learn what it is and how to use it.

## 6.1 FPGA at power up

An FPGA starts un-configured (idle) and every time it's unpowered, it loses its configuration.

If you need to use your FPGA without a PC attached (in standalone mode), that's a problem. The workaround is to configure the FPGA automatically at power-up. The easiest way to do that is with an FPGA boot-PROM – and that's what KNJN boards do.

Here's how it works. The boot-PROM is a small memory that is attached to the FPGA. You program it with an FPGA bitfile. At power-up, the FPGA tries to read the boot-PROM (that's automatic and takes a split-second). If the boot-PROM contains a valid bitfile, the FPGA gets configured. If the boot-PROM is empty or its content is invalid, the FPGA is not configured and stays idle.

After power-up, the boot-PROM gets "out of the way" so that you can always configure the FPGA.

#### 6.2 Boot-PROM and USB

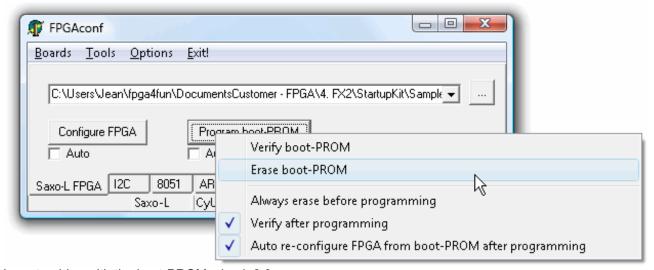

With FPGAconf, the boot-PROM can easily be programmed, verified and erased through USB.

- Programmed: click on the "Program boot-PROM" button.

- Verified or erased: right-click on the button and use the drop-down menu.

If you have troubles with the boot-PROM, check 8.3.

#### 6.3 Boot-PROM and JTAG

The boot-PROM can also be programmed through the FPGA JTAG port.

- For Xilinx FPPAs, check http://www.xilinx.com/bvdocs/appnotes/xapp951.pdf

- For Altera FPGAs, check <a href="http://www.altera.com/literature/an/an370.pdf">http://www.altera.com/literature/an/an370.pdf</a> and also chapter 24 of this document.

# 7 Advanced FPGA control

### 7.1 More FPGA actions

Right-click on the "Configure FPGA" button to see more available FPGA actions:

- Un-configure FPGA.

- Configure FPGA from boot-PROM.

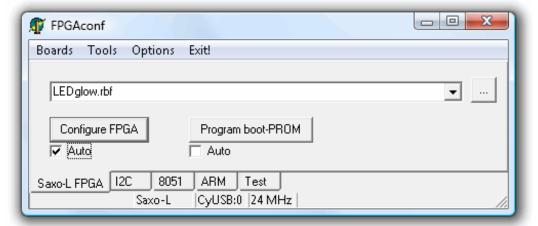

### 7.2 Auto-mode

Two "Auto" check-boxes (below the "Configure FPGA" and "Program boot-PROM" buttons) allow configuring the FPGA or programming the boot-PROM every time the FPGA bitfile is updated on the hard-drive (like when Quartus-II or ISE finishes a compilation).

# 7.3 Options

Go to menu → Options to see the list of options available. Important ones are:

- USB driver. Makes sure this matches the driver installed (see 4.1 and 4.2).

- FX2 clock speed (12, 24 or 48 MHz). This takes effect when FPGAconf configures the FPGA.

FPGAconf saves all settings upon closing.

# 7.4 Log

If you increase the size of the FPGAconf window, you get access to the log panel which remembers and time-stamps each action performed.

# 8 Your own FPGA project

#### 8.1 LEDblink

Here's a simple Verilog source file that makes an LED blink on the board. It is simple and uses only 2 pins so is a good candidate for a first FPGA project.

```

module LEDblink(input clk, output LED);

// first create a 32 bits counter

reg [31:0] cnt;

always @(posedge clk) cnt <= cnt + 1;

// and take one of the counter bit to drive the LED

assign LED = cnt[23]; // here 24th bit... change that to make the LED blink faster or slower

endmodule</pre>

```

To create the FPGA project, follow the instructions from chapter 9 and 10, and make the correct pin assignments using information from chapter 11.

### 8.2 The FPGA doesn't configure?

If FPGAconf fails to configure the FPGA using one of your own FPGA bitfile, check the following:

- Try first with a pre-compiled FPGA bitfile from the startup kit (like LEDblink or LEDglow) since they are known to be good (this makes sure the board works).

- Now with your own FPGA bitfile:

- Make sure all the pin assignments are correct.

- Make sure you followed all the recommendations listed in the chapter 9 or 10 (in particular the one regarding unused pins/IOBs).

## 8.3 The boot-PROM fails to configure the FPGA?

Sometimes you have an FPGA bitfile that works in the FPGA, but when programmed in the boot-PROM, it fails to configure the FPGA.

- First, use one of the FPGA bitfiles from the startup kit (like LEDblink or LEDglow) to program the boot-PROM and make sure it configures the FPGA at power-up.

- Then go back to your own bitfile, and compare its programming properties (Device and Pins options in Quartus, or the Programming File properties in ISE) with a known good project. In particular:

- If you are using Quartus-II, make sure you didn't change the project's programming option (it should be "Active serial").

- If you are using Dragon-E, reduce the Configuration Rate (in ISE "Programming File" properties →

"Configuration Options" tab).

# 9 FPGA projects with Altera's Quartus (Saxo-L/-Q and Xylo/-EM)

To start an FPGA project with Quartus-II, proceed as follows:

- 1. Create a Quartus-II project.

- 2. Go to "Assignments/Device"

- 2.1. Choose the Cyclone family and the "EP1C3T100C8" device (for Saxo-L and Xylo) or the Cyclone-II family and the "EP2C5T144C8" device (for Saxo-Q and Xylo-EM)

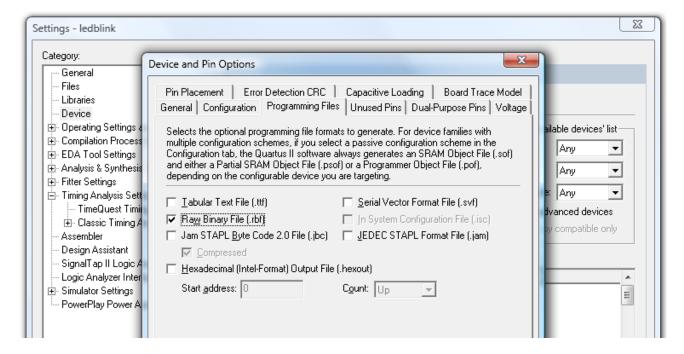

- 2.2. Click on "Device & Pin Options..."

- a) Go to the "Programming Files" tab, select "Raw Binary File (.rbf)". Otherwise, only SOF files are created (SOF files are used in JTAG mode, while RBF files are used in USB mode).

- b) Go to Unused Pins", select "As inputs, tri-stated"

- c) Click "OK"

- 2.3. Click "OK"

- 3. Use the menu  $\rightarrow$  Assignments/Pins and assign the correct pins.

The option 2.2.b is there to prevent the FPGA from driving the pins that are not used in your project (by default, Quartus-II grounds all the unused pins, which often ends-up creating IO contentions). You may change this option back once you know that all the pins of your project are correctly assigned.

For a graphical walk-through, check the Altera Quartus II quick-start quide

# 10 FPGA projects with Xilinx's ISE (Xylo-L/-LM and Dragon-E)

To start an FPGA project with ISE, proceed as follows:

1. Create a new project.

In the New Project Wizard, select the right FPGA for your board:

- Xylo-E: choose "Spartan-6" family and the "XC6SLX9" device in a "TQG144" package.

- Xylo-L/-LM: choose "Spartan3E" family and the "XC3S500E" device in a "PQ208" package.

- Dragon-E: choose "Virtex-5" family with the "XC5VLX20T-1" in "FF323" package.

Optionally, select some source files before finishing the wizard.

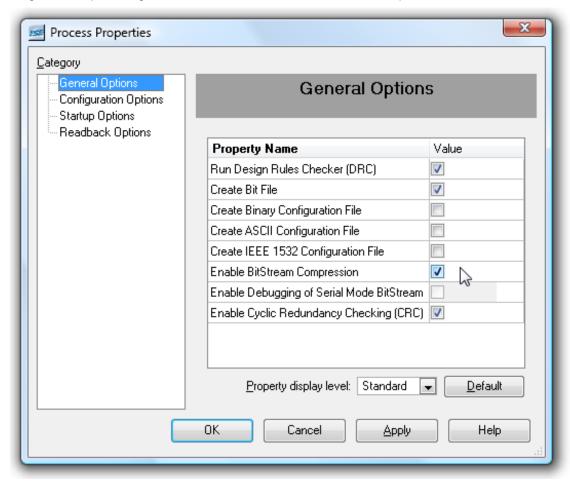

2. Select the top-level design in your project, right-click on "Generate Programming File" and choose "Properties". Select BitStream Compression.

In "Configuration Options", go to "Unused IOB Pins" and choose "Pull Up".

- 3. If you are using Dragon-E, reduce the Configuration Rate (in ISE "Programming File" properties → "Configuration Options" tab) as the maximum speed is not reliable.

- 4. Create a UCF file with the pin assignments.

For a graphical walk-through, check the Xilinx ISE quick-start guide

# 11 FPGA pins

## 11.1 Common pin assignments

This table shows which pins are used for clocks, LEDs and push-buttons.

| Pin name    | FPGA   | Saxo-L | Saxo-Q | Xylo | Xylo-E | Xylo-EM | Xylo-L | Xylo-LM | Dragon-E | Comments                                            |

|-------------|--------|--------|--------|------|--------|---------|--------|---------|----------|-----------------------------------------------------|

| CLK         | Input  | 66     | 17     | 10   | 14     | 17      | 181    | 181     | R9       | Main clock.<br>Software selectable 12, 24 or 48 MHz |

| CLK_ADC     | Input  |        | 88     |      |        |         |        |         |          | 75.7575MHz clock                                    |

| CLK_DIL8    | Input  | 10     | 89 (1) | 34   |        | 91      | 183    | 183     |          | Optional DIL-8 clock oscillator                     |

| CLK_SMD     | Input  |        | 89 (1) |      |        |         | 184    | 184     | V6       | Optional SMD clock oscillator                       |

| CLK_SMD2    | Input  |        |        |      |        |         |        | 80      |          | Second optional SMD clock oscillator                |

| LED1        | Output | 35     | 92 (2) | 91   | 27     | 72      | 146    | 146     | V2       | Active high                                         |

| LED2        | Output |        |        | 97   | 30     | 71      | 147    | 147     | V3       | Active high                                         |

| LED3        | Output |        |        |      |        |         |        |         | D8       | Active high                                         |

| Push-button | Input  |        |        | 92   |        | 63      | 148    | 148     |          | See 11.4                                            |

| vga_h_sync  |        |        |        | 99   |        | 133     |        |         |          | VGA H-sync, active low                              |

| vga_v_sync  |        |        |        | 100  |        | 132     |        |         |          | VGA V-sync, active low                              |

| vga_red     |        |        |        | 2    |        | 112     |        |         |          | VGA red                                             |

| vga_green   |        |        |        | 1    |        | 113     |        |         |          | VGA green                                           |

| vga_blue    |        |        |        | 98   |        | 114     |        |         |          | VGA blue                                            |

Note 1: Do not mount both oscillators, as they share the same board trace and FPGA pin.

Note 2: Shared with DAC\_CTRL1 (see 28.2).

For more pin assignments, check your board layout (chapter 38).

#### 11.2 Clocks

CLK is the main board clock. It is generated by the USB-2 controller (named "FX2" in this document) and is also the clock used by the internal FX2 bus (see paragraph 12.2). CLK defaults at 12MHz at power-up but can also run at 24 or 48MHz (see paragraph 7.3).

You can add more clocks:

- One or several PLL or DLL in the FPGA are available to generate custom frequencies (see your FPGA documentation for details).

- On some boards, a 3.3V oscillator can be added with a specific clock frequency. The oscillator is in DIL-8 (socketable) or SMD5x7 (to solder) form.

- Many other pins can also be used as clock sources. They are shown as CLK, DPCLK, GCLK, GC or CC pins on the chapter 38 drawings.

#### 11.3 LEDs

The LEDs are active high, so to light up an LED, output a "1" (from the right FPGA pin – see table above).

Note that when the FPGA is not configured, the LEDs glow slightly (because of weak-pullups in the FPGA IOs that are then activated).

#### 11.4 Push-button

The push-button is an input to the FPGA.

- It is usually active low (reads as "1" when the push-button is not pressed, and "0" when it is).

- On newer board Xylo revision H and Xylo-L/-LM revision D and above, it is active high (reads as "0" when the push-button is not pressed, and "1" when it is).

# 11.5 VGA (Xylo/-EM only)

The VGA interface uses five FPGA pins and is able to generate eight colors on a VGA monitor. The <u>pong</u> and <u>breakout</u> games provide example designs that make use of the VGA output.

To connect a VGA monitor, solder a <u>DB-15HD</u> connector on your board.

### 11.6 Secondary connector

The secondary connector is a small connector that has only four pins. It provides power plus two IOs. On some boards, the two IOs have serial terminations, plus weak over-voltage protections:

- Serial terminations: useful for high-speed serial output signals (like a graphic LCD, chapter 25).

- Weak over-voltage protection: useful for a low speed I2C bus.

Note that Dragon-E has two secondary connectors (one of them powered with +5V and the other by +3.3V).

| Connector pin        | Xylo | Saxo-L | Saxo-Q | Xylo-E | Xylo-EM | Xylo-L /<br>Xylo-LM | Dragon-E<br>bottom | Dragon-E<br>top | Comment                                             |  |

|----------------------|------|--------|--------|--------|---------|---------------------|--------------------|-----------------|-----------------------------------------------------|--|

| 1. VCC               | +5V  | +5V    | +5V    | +3.3V  | +5V     | +5V                 | +5V                | +3.3V           | Power pin                                           |  |

| 2. IO1               | 65   | 91     | 143    | 83     | 64      | 193                 | T12                | T16             | RxD or serclk or other                              |  |

| 3. IO2               | 68   | 97     | 144    | 84     | 57      | 196                 | U10                | V15             | TxD or serdata or other                             |  |

| 4. GND               | 0V   | 0V     | 0V     | 0V     | 0V      | 0V                  | 0V                 | 0V              | Power pin                                           |  |

| Termination/<br>WOVP | Yes  | Yes    | No     | No     | Yes     | Yes                 | No                 | No              | Serial termination and weak over-voltage protection |  |

# 11.7 Text LCD (Saxo-L & Xylo/-E only)

See chapter 30 for more info.

## 11.8 I2C (all boards)

The I2C bus is connected to the FX2 hard-macro I2C controller. See chapter 16 for details.

On Xylo, the I2C bus is internally connected to the FPGA pins 51 (SDA) and 52 (SCL).

On Saxo-L/-Q and Xylo-E/-EM/-L/-LM, the I2C bus is not internally connected to the FPGA. You can connect the FPGA to the I2C bus externally by using wires or an I2C switch that links the secondary connector to the I2C connector. Then configure the FPGA with a soft I2C controller (master or slave).

Check KNJN's I2C accessories page for I2C switches and other peripherals.

# 11.9 Ethernet signals (Xylo/-E/-EM/-L/-LM only)

For Xylo-E, an optional Ethernet adapter is available. The other boards have one or two dedicated Ethernet headers. Each header uses three FPGA pins named RD, TDp and TDn.

| Pin names       | Xylo     | Xylo-L        | Xylo-LM       | Xylo-EM       |

|-----------------|----------|---------------|---------------|---------------|

| RD1, TDp1, TDn1 | 21, 3, 4 | 150, 151, 152 | 150, 151, 152 | 143, 139, 142 |

| RD2, TDp2, TDn2 |          |               | 77, 78, 82    |               |

# 11.10 HDMI (Xylo-E only)

Check the "StartupKit\FPGA project - HDMI" folder.

# 11.11 SD card (Xylo-E only)

The SD card is an Xylo-E option that mounts on the bottom of the board. Check the "StartupKit\FPGA project – SD" folder for more details.

## 12 USB/FX2 interface

The USB interface makes using your FPGA board easy as it allows to:

- 1. Configure the FPGA

- 2. Communicate with the FPGA (once it is configured).

This chapter describes the communication with the FPGA. Chapter 13 describes the PC function calls and chapter 14 gives complete examples of communication.

Your board uses a Cypress CY7C68013 high-speed USB-2 chip (nicknamed "FX2") that is the interface between the PC's USB-2 link and the FPGA. It achieves typical application level speeds of 30MB/s to 40MB/s (240Mbps to 320Mbps).

#### 12.1 Bulk vs. Isochronous

The USB protocol defines two types of data packets:

- Bulk packets (guaranteed delivery)

- Isochronous packets (guaranteed bandwidth)

Bulk packets guarantee delivery, which means that if there is an error on the line, the data is retransmitted automatically until it is received correctly. This is done in the background at the USB hardware level, so that the FPGA ends up only receiving guaranteed good data from the PC, and the PC ends up receiving guaranteed good data from the FPGA. Note that bulk packets can only be up to 512 bytes long (for the USB 2.0 high-speed mode used by the FX2), but multiple of them are automatically sent back-to-back for longer transmissions.

Isochronous packets don't guarantee delivery, so KNJN FX2 boards use bulk packets exclusively.

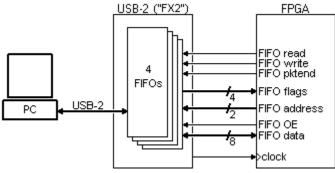

### 12.2 FX2 interface and FIFOs

The FX2 is connected to the FPGA through an 8bit bidirectional data bus, a clock, and a few extra signals.

The FX2 implements four hardware FIFOs, named FIFO2, FIFO3, FIFO4 and FIFO5.

- FIFO2 and FIFO3 are used to send (i.e. PC → FPGA). The PC (through the USB link) writes to these FIFOs, and the FPGA reads from them.

- FIFO4 and FIFO5 are used to receive (i.e. PC ← FPGA). The FPGA writes to these FIFOs, and the PC (through the USB link) reads from them.

- Each FIFO can hold up to 1024 bytes of data (or more precisely two times 512 bytes, more details later).

#### 12.3 PC to FPGA

When the PC software sends data to FIFO2 or FIFO3, it specifies how many bytes to send. Anything bigger than 512 bytes is automatically sliced on the USB line, so the FPGA doesn't need to be aware of the USB packets boundaries.

#### 12.4 FPGA to PC

When the FPGA wants to send data to the PC, it writes data to FIFO4 or FIFO5. What happens if the FPGA wants to send less than 512 bytes?

- The FPGA can keep writing (dummy data) until it reaches 512 bytes (padding method).

- The FPGA can assert a special line named "FIFO pktend" that signals to the FX2 that a packet is complete.

#### Note that:

- Data is committed to the FIFO (and available for the PC to read) only when one of the two previous conditions is met.

- Each FIFO can hold 2 packets. So each FIFO can hold up to 1024 bytes, but may be full by having less than that if the packets are completed using "FIFO pktend".

## 12.5 FIFO flags

The FX2 provides one flag signal per FIFO. The flags are named FLAG2, FLAG3, FLAG4 and FLAG5.

- FLAG2 and FLAG3 are "empty" flags. They indicate that FIFO2 and FIFO3 are empty

- FLAG4 and FLAG5 are "full" flags. They indicate that FIFO4 and FIFO5 are full.

The flag signals are read by the FPGA. The FPGA controls when it reads and writes from the FIFO, but it has to follow these rules:

- The FPGA can only read from FIFO2 or FIFO3 if it is not empty.

- The FPGA can only write to FIFO4 or FIFO5 if it is not full.

### 12.6 FIFO data, address and control lines

The FPGA controls which FIFO he accesses using a 2-bits wide address bus named "FIFO address".

| FIFO address | FIFO accessed |

|--------------|---------------|

| 00           | FIFO2         |

| 01           | FIFO3         |

| 10           | FIFO4         |

| 11           | FIFO5         |

#### Note that:

- The FPGA reads from FIFO2/FIFO3 by addressing one of them and asserting the "FIFO read" signal.

- The FPGA writes to FIFO4/FIFO5 by addressing one of them and asserting the "FIFO write" signal. While writing, the FPGA can signal the end of a packet using the "pktend" signal.

- The FPGA reads and writes to the FIFOs using the bidirectional 8bit wide data bus "FIFO data". The FPGA also controls "FIFO OE" (which tells the FX2 to drive the data bus or not).

### 12.7 FIFO signal names

Here's the complete list of signals used internally by the FPGA to access the FX2 FIFOs.

- All are active high.

- For examples of use, check chapter 14.

| Signal name                             | Width  | Direction  | Purpose                                                     |

|-----------------------------------------|--------|------------|-------------------------------------------------------------|

| FIFO_CLK                                | 1 bit  | FX2 → FPGA | Clock (all the other signals are synchronous to this clock) |

| FIFO_RD                                 | 1 bit  | FPGA → FX2 | FPGA reads from FX2                                         |

| FIFO_WR                                 | 1 bit  | FPGA → FX2 | FPGA writes to FX2                                          |

| FIFO_PKTEND                             | 1 bit  | FPGA → FX2 | FPGA indicates "End of packet" (i.e. FPGA is done writing)  |

| FIFO_DATAIN_OE                          | 1 bit  | FPGA → FX2 | FPGA wants the FX2 to drive the DATA bus                    |

| FIFO_DATAOUT_OE                         | 1 bit  | internal   | FPGA drives the DATA bus                                    |

| FIFO_DATAIN                             | 8 bits | FX2 → FPGA | Data from FX2                                               |

| FIFO_DATAOUT                            | 8 bits | FPGA → FX2 | Data to FX2                                                 |

| FIFO_FIFOADR                            | 2 bits | FPGA → FX2 | FPGA selects one FX2 FIFO (out of the four available)       |

| FIFO2_empty / FIFO2_data_available      | 1 bit  | FX2 → FPGA | FIFO2 is empty, or not                                      |

| FIFO3_empty / FIFO3_data_available      | 1 bit  | FX2 → FPGA | FIFO3 is empty, or not                                      |

| FIFO4_full / FIFO4_ready_to_accept_data | 1 bit  | FX2 → FPGA | FIFO4 is full, or not                                       |

| FIFO5_full / FIFO5_ready_to_accept_data | 1 bit  | FX2 → FPGA | FIFO5 is full, or not                                       |

# 13 PC access to the FX2 FIFOs

The PC (through the USB link) can write to FIFO2/3 and read from FIFO4/5. Depending of the USB driver installed (chapter 4), you must use a different set of software functions.

## 13.1 FIFO access with the CyUSB driver

The PC reads and writes to the FIFOs using the XferData C++ method:

```

bool XferData(PUCHAR buf, LONG &len)

```

When writing, the len parameter specifies how many bytes we are sending to the FPGA. For example, let's send one byte to FIFO2:

```

unsigned char c = 41;

LONG len = sizeof(c);

BulkOutPipe2->XferData(&c, len); // send one byte (41) to FIFO2

```

The XferData method is also used for reading from FIFO4/5. In that case, the len parameter value must be the size of the data packet returned by the FX2, or a bigger value. In doubt, always use a multiple of 512 to avoid underflow problems.

For example:

```

unsigned char buf[512];

LONG len = sizeof(buf);

BulkInPipe4->XferData(buf, len); // read up to 512 bytes

// now len contains the number of bytes actually read

```

#### 13.2 FIFO access with the EzUSB driver

The PC writes to the FX2 FIFO2/3 using a C function like:

```

void USB_BulkWrite(ULONG pipe, void* buffer, WORD buffersize) // pipe must be 2 or 3

```

The PC reads from the FX2 FIFO4/5 using a C function like:

```

WORD USB_BulkRead(ULONG pipe, void* buffer, WORD buffersize) // pipe must be 4 or 5

```

With USB\_BulkRead, the buffersize parameter value must be the size of the data packet from the FX2, or a bigger value. In doubt, use a multiple of 512 to avoid underflow problems.

The "pipe" number is the FIFO number. So to write to FIFO3, we could use

```

char* str = 'hello';

USB BulkWrite(3, str, strlen(str)); // write the 5 bytes string "hello" to FIFO3

```

# 14 FX2 examples

# 14.1 Example 1: LED control

This is the simplest of our examples. We control the board's LEDs through USB-2.

Let's use FIFO2. Every time a byte is sent from the PC to FIFO2, the FPGA reads it and updates the LEDs.

The C code looks like this:

The Verilog HDL looks like this:

The complete code is available in the startup kit ("Projects\USB-2 (FX2) 1 - Blink leds").

## 14.2 Example 2: Text LCD

This second example controls a text LCD display connected to the board. See chapter 30 for details on how to make the connection.

In our implementation, any data sent by the PC to FIFO2 is read by the FPGA and sent to the LCD. The FPGA uses a small state machine (just 2 states) to control how to read from FIFO2.

USB transmits data much faster than the LCD can accept it. This example assumes that the PC sends the bytes to the LCD one by one - not very efficient from the USB point of view, but this keeps this example simple.

For LCD command bytes, we send 0x00 followed by a command byte. It is ok to send the 2 bytes at once (in the same USB packet) because the first one (0x00) is not sent to the LCD module but is just there to indicate to the FPGA that the second byte is a command to the LCD.

The C code looks like this:

```

void main()

{

USB_Open();

// Commands - Initialize the LCD

USB_WriteWord(0x3800);// remember, the PC is little-endian, so that's 0x00 followed by 0x38 !!

USB_WriteWord(0x0F00);

USB_WriteWord(0x0100);

Sleep(2);

// Data

USB_WriteChar('X');

USB_WriteChar('y');

USB_WriteChar('i');

USB_WriteChar('o');

USB_WriteChar('o');

}

```

The complete code is available in the startup kit ("Projects\USB-2 (FX2) 2 - Text LCD display").

### 14.3 Example 3: Bidirectional communication

Here the FPGA waits until some data is available in FIFO2. It counts the number of bytes available and sends the count back to FIFO4.

The HDL code looks like this:

```

req [2:0] state;

always @ (posedge FIFO CLK)

case(state)

3'b000: if( FIFO2_data_available) state <= 3'b001; // wait for data packet in FIFO2

3'b001: if(~FIFO2 data available) state <= 3'b100; // wait until end of data packet

3'b100: state <= 3'b101; // switch to FIF04, turnaround cycle 3'b101: state <= 3'b110; // write data 3'b110: state <= 3'b000; // end packet, turnaround cycle

default: state <= 3'b000;</pre>

endcase

assign FIFO FIFOADR = {state[2], 1'b0}; // FIFO2 or FIFO4

assign FIFO RD = (state==3'b001);

// count the number of bytes received

reg [7:0] cnt;

wire read byte = (state==3'b001) & FIFO2 data available;

always @(posedge FIFO CLK) if(read byte) cnt <= cnt+8'h1;

// now write the count back to FIFO4

assign FIFO DATAOUT = cnt;

assign FIFO WR = (state==3'b101);

assign FIFO_PKTEND = (state==3'b110);

assign FIFO DATAIN OE = ~state[2];

assign FIFO DATAOUT OE = (state==3'b101);

```

Care needs to be taken so that FIFO\_DATA\_IN and FIFO\_DATA\_OUT are never driven together (to avoid a data bus contention). Other timing issues may need to be reviewed. For example, it may be wise to have one idle clock cycle (when nobody's driving the bus) during a bus turnaround, especially before allowing the FPGA to drive the DATA bus when the FPGA just read from the FX2. Refer to the FX2 datasheet for timing information.

The complete code is available in the startup kit ("Projects\USB-2 (FX2) 3 - Bidirectional communication").

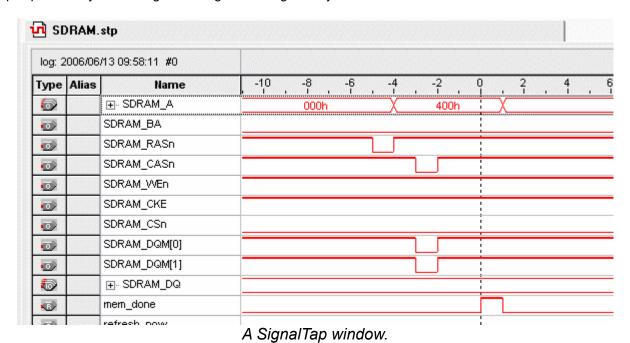

# 14.4 Example 4: SDRAM (Xylo-EM/LM only)

The example shows one simple way to read and write to the SDRAM from the PC. The SDRAM is used in AUTO-PRECHARGE mode with burst length=1, CAS latency=2.

The source code is available in the startup kit ("FPGA Project - USB-2 (FX2) 4 - SDRAM").

Note: this FX2 SDRAM design is not provided for Xylo-E. Instead a more complete SDRAM controller is provided (similar to the design published on <a href="mailto:this fpga4fun's page">this fpga4fun's page</a>).

# 14.5 Example 5: DDS (Saxo-Q only)

This example shows how to create and control a DDS in the FPGA.

The source code is available in the startup kit ("FPGA Project - USB-2 (FX2) 5 – DDS"). See also fpga4fun's <u>DDS project</u> for more information.

# 15 Ethernet (Xylo-E/-EM/-L/-LM only)

## 15.1 Ethernet board setup

With Xylo-EM/-L/-LM, solder a PulseJack RJ-45 connector to the board.

With Xylo-E, connect an Ethernet adapter to the secondary connector.

Use a regular network cable from a network hub/switch to the RJ-45. If you want to connect your board directly to a PC, use a "crossover" network cable.

### 15.2 Ethernet HDL reference design

A reference design is provided allowing bi-directional 10BASE-T communication. The reference design is provided in source code form only.

The design provides an example of UDP/IP transmission and reception.

- Transmission: a packet is sent at regular intervals (about one every second).

- Reception: every time a UDP packet is received, the board checks the packet validity and updates its LEDs (the first 2 bits of the UDP payload are used to update the 2 LEDs). The packet payload is also stored and sent back in the transmission packets.

**Important:** The reference design requires a 24MHz clock. Make sure FPGAconf's clock option is set correctly (see paragraph 7.3 - FX2 clock speed).

### 15.3 Troubleshooting – the PC has troubles receiving

- Make sure the hub/switch light blinks every second or so, to indicate that a packet is transmitted by the board

- Make sure you are not running a firewall on the PC

## 15.4 Troubleshooting – the PC has troubles sending

Make sure the PC has the correct ARP entries. You can use "ARP –a" to check the ARP entries. The physical address of the board should be listed. If it is not, you can add it manually using "ARP" or "netsh". See below examples when the FPGA uses IP 192.168.0.44 and physical address 00-12-34-56-78-90

| os                           | Command                                                                                                |

|------------------------------|--------------------------------------------------------------------------------------------------------|

| Windows XP                   | ARP -s 192.168.0.44 00-12-34-56-78-90                                                                  |

| Windows Vista to Windows 8.1 | netsh interface ipv4 add neighbors "Local Area Connection" 192.168.0.44 00-12-34-56-78-90              |

| Windows 10                   | netsh interface ipv4 add neighbors Ethernet 192.168.0.44 00-12-34-56-78-90                             |

|                              | tip 1: for Wi-Fi, replace "Ethernet" by "Wi-Fi" tip 2: to remove an address, replace "add" by "delete" |

- With Windows XP, an additional IP parameter can be used in the ARP -s command to specify the IP of the

interface where your FPGA board is plugged. This may be required if your machine has multiple Ethernet ports

that are enabled concurrently.

- With Windows Vista and above, make sure you open an administrator command-line prompt (otherwise the netsh command fails). An administrator command-line prompt can be easily opened by typing "cmd" into the start menu search box, and then pressing Shift+Ctrl+Enter.

### 15.5 UDP tester

Use FPGAconf Tools  $\rightarrow$  UDP tester, or the UDP utility found at the bottom of <u>this page</u>, or the Ethernet UDP sample C code from chapter 37.

```

Waiting for packets (Press Ctrl-C to exit)...

Received 18 bytes from 192.168.0.44

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11

Received 18 bytes from 192.168.0.44

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11

Received 18 bytes from 192.168.0.44

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11

Received 18 bytes from 192.168.0.44

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11

Received 18 bytes from 192.168.0.44

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11

```

# 16 I2C bus

### 16.1 I2C controller

The board has an integrated I2C bus controller. The controller is a "hard macro" (the hardware is built into the FX2), as opposed to a "soft macro" I2C controller that can be programmed into the FPGA.

#### 16.2 On board devices

The following devices share the I2C bus:

- I2C "hard macro" controller (USB chip).

- I2C connector (to connect to external devices through an I2C cable).

- I2C EEPROM (optional on some boards, but can be added if missing see chapter 17).

- The FPGA (see paragraph 11.8 for details).

Please note that to be able to communicate with the I2C bus, the FPGA needs to be configured with a "soft macro" I2C controller.

For example, here's Xylo controlling an external 7-segments led display I2C board.

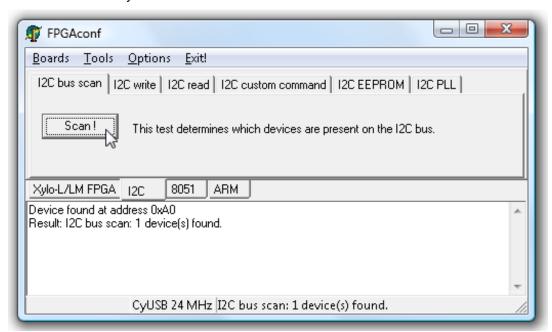

An I2C "control panel" is part of FPGAconf. It can issue these commands:

- I2C Bus scan

- I2C Write

- I2C Read

- I2C Custom command (multiple reads/writes packet)

- I2C PLL

#### 16.3 Bus scan

The bus scan is useful to discover what devices are present on the I2C bus.

Note that only devices that respond to I2C write commands are scanned. Most I2C devices respond to both reads and writes, so they can be discovered by the bus scan.

Note: some I2C devices (like the 24LC00 EEPROM) respond at multiple addresses.

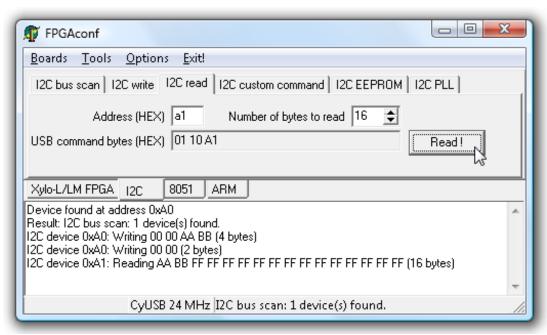

### 16.4 Write & Read

#### 16.5 Custom commands

Custom commands allow issuing multiple reads & writes in the same command. It also uses I2C restart signals in between each read and write.

See the paragraph 20.3 for the Command packet required to create such commands.

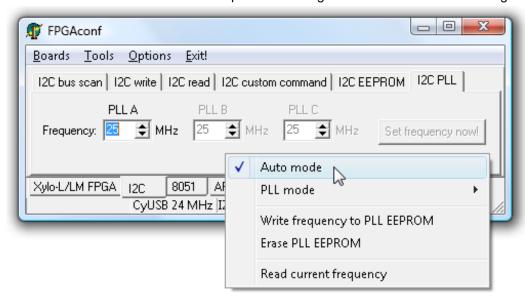

#### 16.6 PLLs

I2C PLLs can be connected to the I2C bus. The I2C control panel allows direct control of the PLLs (up to three PLLs can be controlled from the control panel).

Additional PLL commands are available from the PLL option menu. Right-click on the PLL window to get the option menu.

Check KNJN's I2C PLLs page for more info.

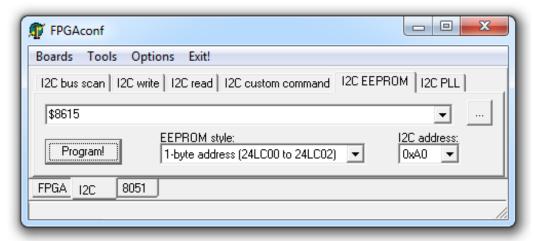

### 16.7 EEPROM

FPGAconf can program I2C EEPROMs easily. Go to the "EEPROM" tab, select a ".bin" file and click "Program!". See chapter 17 for EEPROM application details.

# 17 I2C EEPROM

### 17.1 EEPROM purposes

One characteristic of the USB-2 FX2 chip is that, at power-up, it accesses the I2C bus and looks for an EEPROM.

An EEPROM can be used for three purposes:

- 1. Change the USB ID

- 2. Change the USB ID, and load code into the FX2 8051 (chapter 19)

- 3. Store data

All boards have an EEPROM footprint but the EEPROM component may or may not be present. If it is not, you can either solder one, or use an adapter board (17.2).

The EEPROM on your board is as follows:

| Board                       | EEPROM present by default? | EEPROM style    | I2C address | Typical EEPROM used   |

|-----------------------------|----------------------------|-----------------|-------------|-----------------------|

| Xylo-E                      | No                         | 1-byte address  | 0xA0        | 24LC00 SOT23          |

| Xylo-L / Xylo-LM / Dragon-E | Yes                        | 1-byte address  | 0xA0        | 24LC00 or 24LC02 SO-8 |

| Saxo-L / Xylo / Xylo-EM     | No                         | 2-bytes address | 0xA2        | 24LC32 or 24LC64 SO-8 |

| Saxo-Q                      | Yes                        | 2-bytes address | 0xA2        | 24LC32 or 24LC64 SO-8 |

An EEPROM using the I2C addresses shown above allows changing the FX2 USB ID (chapter 18). Also some EEPROMs (like the 24LC00) respond to multiple addresses, so will be detected multiple times by an I2C Bus scan.

## 17.2 EEPROM adapter board

If soldering an EEPROM is not possible or desirable, an EEPROM adapter board can be used, like KNJN's item 1402.

An adapter board allows choosing the EEPROM I2C address, but if you need to adjust the FX2 USB ID (chapter 18) or load code from the EEPROM to the 8051, the address needs to be set to the one shown above. For example, with a 24LC64, be sure to use an I2C address of 0xA2.

If you are only interested in storing data in the EEPROM, other I2C addresses could be used as well.

### 18 USB IDs

#### 18.1 Custom IDs

If your KNJN FX2 board has an I2C EEPROM (chapter 17), you can change the board's USB ID easily: go to the I2C EEPROM window and enter a dollar sign followed by the desired ID (four hex digits). So for example, the string \$8615 means ID 8615.

Then select the right EEPROM style and I2C address, and click "Program!"... Voila, the next time you plug-in the board, Windows will look for a driver with this new USB ID.

Be careful: if you program a custom ID and you don't have a matching driver, you can render your board inaccessible.

What happened? FPGAconf programmed eight specially crafted bytes into the EEPROM. Then at power-up, the FX2 reads the EEPROM to decide what USB ID to use.

For example, for ID 8615, the sequence C0 B4 04 15 86 00 00 04 is programmed (see FX2 documentation for the explanation of each byte).

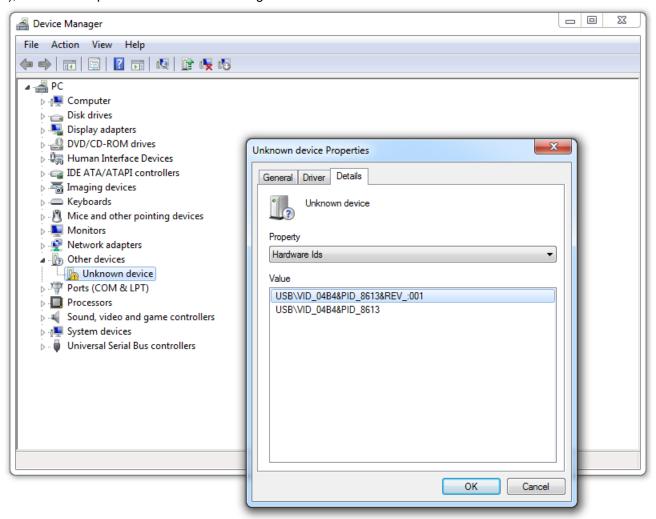

#### 18.2 Default IDs

By default (i.e. if the EEPROM is missing or empty), the USB IDs of the FX2 chip are:

- Vendor ID: 04B4 (Cypress Semiconductor)

- Device ID: 8613 (no EEPROM default ID for EZ-USB FX2)

If the EEPROM is present, it is either empty (the board uses use ID 8613) or factory programmed to use Device ID 8614.

As you can see, a USB ID consists of two numbers: a Vendor ID and a Device ID. But the Vendor ID of all the USB drivers provided by KNJN is always the same (04B4), while the Device ID is variable. So when we mention the USB ID in the rest of this document, we are in fact referring only to the USB Device ID.

#### 18.3 hex2bix

Cypress provides a utility named "hex2bix" (in the FX2 development kit) that can be used to generate EEPROM contents. For example, use the following command to generate a file "id.bin" with Vendor ID 04B4 and Device ID 8615:

hex2bix.exe -i -f 0xC0 -v 0x04B4 -p 0x8615 -o id.bin

Then program "id.bin" into the EEPROM using FPGAconf: go to the "EEPROM" tab, select "id.bin" and click "Program!".

#### 18.4 USB-IF

Official USB IDs are maintained by the USB-IF. To get a new official ID, see <a href="http://www.usb.org/developers/usbfag/">http://www.usb.org/developers/usbfag/</a>

# 18.5 Checking the USB ID of a plugged board

The device manager shows the ID used by any plugged board. The board doesn't even need to be recognized (driver loaded), see for example an unknown board using the device ID 8613.

# 19 8051

### 19.1 8051 processor

The FX2 chip (CY7C68013) has an 8051 processor used for initialization and housekeeping.

Of most interest:

- The 8051 can force the FX2 to re-enumerate with different USB-IDs. See for example paragraph 23.4.

- The FX2 is connected to the FPGA, so the 8051 can be programmed to communicate with the FPGA.

### 19.2 8051 programming

The 8051 CPU is attached to an 8KB RAM (or 16KB RAM with the more recent CY7C68013A) where the 8051 code is stored.

The 8051 control panel is used to load code into the RAM.

- 1. Select a ".hex" file (this is generated by an 8051 assembler, see next paragraph)

- 2. Click on "Program!"

Under Linux, you can also use fxload:

1. Locate your FX2 board using

lsusb

2. Locate the device. Depending on your Linux distribution, it is in

/proc/bus/usb/00x/00x

/dev/bus/usb/00x/00x

3. Load the code in the FX2 using something like

fxload -I firmware.hex -D /proc/bus/usb/00x/00x -t fx2

Note that you may need administrator privileges.

### 19.3 HEX files

or

To create hex files for the FX2, you need an 8051 compiler/assembler, like:

- The Cypress FX2 development kit (see 33.2).

- The SDCC cross-C compiler.

## 19.4 Power-up

The I2C EEPROM (chapter 17) can be programmed with code that runs automatically in the 8051 at power-up. The first byte of the EEPROM is 0xC2 in this case.

As an example, try the file "Sample files - I2C EEPROM\EEPROM FX2 CPU 24MHz.bin". It makes the 8051 default to 24MHz instead of 12MHz. Check the FX2 development kit for more details on how to create ".bin" files.

# 20 I2C-over-USB protocol

## 20.1 Background

The I2C bus is controlled from the PC through the USB link.

While you issue I2C reads and writes with the I2C control panel, the PC sends and receives some special USB I2C command and response bytes. They are normally hidden, but FPGAconf can display them on demand (right-click in the I2C panel to see the "I2C LOG options").

You can also write a user application that sends the commands directly. That allows writing custom I2C applications. A description of the protocol is given below, as well as in the startup kit ("Sample files - I2C control").

#### 20.2 Protocol

The protocol is packet based. To issue an I2C action, you need to:

- 1. Send an I2C command packet.

- 2. Read the I2C response packet.

Command packets are sent to USB-2 pipe 0, and response packets are read from USB-2 pipe 1.

See the "Sample files - I2C control" files for more information.

## 20.3 Command packet

A command is defined as a series of blocks, each block being a read or write request.

First byte: number of blocks

Then for each block, a few bytes:

- If I2C read: number of bytes to read, plus I2C address (with LSB=1 to indicate a read). On return, we get one status byte plus the data read.

- If I2C write: number of bytes to write (including the I2C address), followed by the I2C address (with LSB=0), plus

the bytes to write.

On return, we get one status byte.

# 20.4 Response packet

The length of the response usually equals the number of command blocks sent (you get one status byte for each block in the command), in addition to the data returned for each read block.

Each status byte is:

- bit 7: BERR (bus error), indicates a bus contention (another I2C master took control of the bus).

- bit 6: ACK, set if the device is present, cleared if the device didn't respond, or asked to stop.

- bit 5..0: byte count (number of bytes written or read).

During processing, if any block results in an error (BERR or no ACK), the I2C controller stops at this particular block and doesn't process any additional block in the packet. So in this case, the length of the response may be lower than expected, and the last response status byte shows the error.

#### 20.5 Restrictions

- A command can consist of as many read and write blocks as you wish, as long as the command packet total length doesn't exceed 64 bytes.

- A response packet total length can't exceed 64 bytes either. So if the command has reads, make sure you don't

read too much because the response packet length must fit in 64 bytes.

# 20.6 I2C start/restart/stop

A command is initiated with an I2C "start" sequence. Then if more than one block is used, I2C "restart" sequences are used between blocks. Finally a single I2C "stop" sequence is sent at the end of the command.

# 21 JTAG FPGA configuration

### 21.1 Configuration files

Depending on the FPGA configuration interface used, different file types are required.

| FPGA   | Interface        | Preferred software | File to use  |

|--------|------------------|--------------------|--------------|

| Altera | USB or boot-PROM | FPGAconf           | ".rbf" (RBF) |

| Altera | JTAG             | Quartus-II         | ".sof" (SOF) |

| Xilinx | USB or boot-PROM | FPGAconf           | ".bit" (BIT) |

| Xilinx | JTAG             | iMPACT             | ".bit" (BIT) |

Refer to chapters 9 and 10 to learn how to generate the configuration files.

### 21.2 JTAG FPGA configuration with Altera's Quartus-II

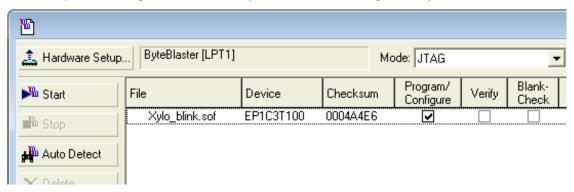

- 1. Make sure the JTAG connection is activated with a JTAG cable or JTAG-over-USB (paragraph 22.2).

- 2. In Quartus-II, open the "Programmer" window (in menu → Tools/Programmer).

- 3. Click on the "Hardware Setup" button and select the JTAG cable you're using (usually a ByteBlaster/-II or USB-Blaster).

- 4. Select "JTAG" in the "Mode" drop-down list.

- 5. Load the ".sof" file.

- 6. Check the "Program/Configure" check-box and click "Start".

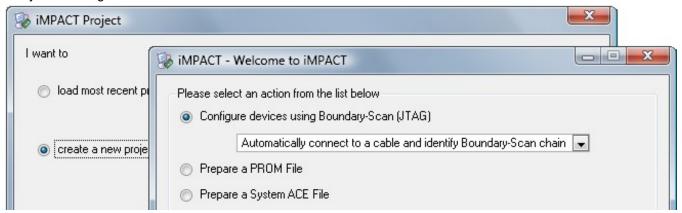

# 21.3 JTAG FPGA configuration with Xilinx's ISE

- 1. Check chapter 38 to find the location of the FPGA JTAG header on your board. Connect a JTAG cable to the JTAG header (suitable JTAG cables include the <u>USB</u> or <u>Parallel</u> Xilinx cables, and <u>KNJN JTAG cables</u>).

- 2. Run the <u>iMPACT</u> software (which is part of Xilinx's ISE). Select "create a new project" and then automatic JTAG discovery. If your JTAG cable is connected correctly, iMPACT detects your JTAG chain automatically and allows you to configure the FPGA.

# 22 JTAG FPGA support in Altera's Quartus-II

### 22.1 JTAG

In addition to FPGA configuration (chapter 21), the FPGA JTAG port allows you to take advantage of Quartus-II's advanced JTAG features, like

- Boot-PROM programming (see chapter 24)

- SignalTap® II logic analyzer

SignalTap is particularly interesting as it brings a free logic analyzer to the FPGA.

### 22.2 JTAG connection

There are two ways to use JTAG with Altera's FPGAs:

- 1. JTAG-over-USB (see chapter 23).

- 2. JTAG connector (with an external JTAG cable, see 22.3).

The advantage of using JTAG-over-USB is that you don't need a separate JTAG cable. The disadvantage is that it ties down the USB port. So if you want to take advantage of the high-speed FX2 USB-2 port, and still have JTAG access, you need to use the JTAG connector with an external JTAG cable.

### 22.3 JTAG connector

The JTAG connector is used with an external JTAG cable (like a ByteBlaster II or USB-Blaster).

For Altera boards, the JTAG connector is a 10 pin (2x5) <u>shrouded connector</u> (on Xylo-EM, use a right-angle connector to avoid mechanical troubles if a FlashyD board is mounted).

# 23 JTAG-over-USB for Altera FPGAs

#### 23.1 Protocol emulation

With JTAG-over-USB, you can emulate an Altera JTAG cable like a USB-Blaster, or any other JTAG protocol you might have in mind.

The KNJN boards JTAG-over-USB support is based on the USB JTAG adapter open source project published at <a href="http://www.ixo.de/info/usb\_jtag/">http://www.ixo.de/info/usb\_jtag/</a>

### 23.2 Board support

Saxo-L/-Q and Xylo-L/-LM/-EM are pre-wired for the USB JTAG open source project, so they can use JTAG-over-USB without modification (go to 23.4).

Xylo require a preparation first (23.3).

# 23.3 Non pre-wired boards

With Xylo, JTAG-over-USB can be used once four wires have been soldered on the board. These four wires are used to connect the FX2 (port D) to the JTAG connector.

|        | JTAG function | JTAG connector pin | FX2 pin   |

|--------|---------------|--------------------|-----------|

| Wire 1 | TCK           | 1                  | 1 (PD.5)  |

| Wire 2 | TDO           | 3                  | 2 (PD.6)  |

| Wire 3 | TMS           | 5                  | 3 (PD.7)  |

| Wire 4 | TDI           | 9                  | 56 (PD.4) |

#### Notes:

- For the JTAG connector, check the Xylo layout drawing (paragraph 38.1).

- The wires may be hard to solder directly on the FX2 (the FX2 package pin pitch is small). On the latest Xylo board revisions (rev. F and later), the pin signals are also available on the bottom of the board, below the FX2, which makes the connections much easier to make.

- The FX2 WAKEUP pin (pin 51) may need to be high for the FX2 to re-enumerate reliably in JTAG-over-USB mode, but the boards default to low. A resistor jumper on the bottom of the boards allows the WAKEUP level to be changed.

### 23.4 Switch to JTAG-over-USB mode

Switching to JTAG-over-USB mode is just a matter of loading a file into the 8051. Compiled files are provided in the "Sample files – 8051" directory. Loading a file into the 8051 FX2 is simple, see paragraph 19.2. Once loaded, the PC beeps (re-enumerates the USB device) and you are ready to use Quartus-II built-in JTAG support.

Two versions of the JTAG-over-USB files are provided: full-speed (12mbps) or high-speed (480mbps). Try the high-speed version first, and switch to the other one in case you run into trouble.

Note that the first time the PC sees a device in JTAG-over-USB mode, it asks for the USB-Blaster driver. The driver can be found in your Quartus installation directory (usually something like C:\altera\xx\quartus\drivers\usb-blaster). More info is available on this page.

## 24 JTAG boot-PROM programming with Altera's Quartus-II

### 24.1 Create the JTAG Indirect Configuration File

The JTAG indirect mode allows programming the boot-PROM through JTAG.

- 1. In Quartus-II, go to "File/Convert programming file"

- 2. In the "Output programming file" panel, select

- a) Programming file Type = "JTAG Indirect Configuration File (.jic)"

- b) Configuration device = "EPCS1" (Xylo) or "EPCS4" (Saxo-Q/Xylo-EM) for the boot-PROM 1 or 4Mbit

- c) File-name = a ".jic" file name of your choice

- 3. In "Input file to convert", select

- a) Flash loader: Cyclone (Xylo) or Cyclone-II EP2C5 (Saxo-Q/Xylo-EM)

- b) SOF Data: SOF file that you want to use for the boot-PROM

- 4. Click "OK"

This creates the ".jic" file.

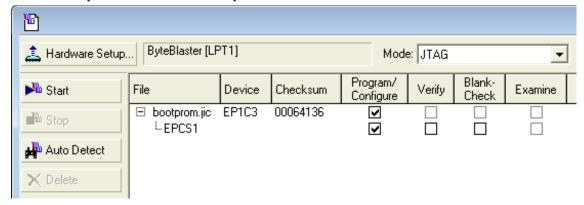

### 24.2 Program the boot-PROM

Now we can use the ".jic" file to program the boot-PROM.

- 1. Load the "Programmer" window (in Tools/Programmer)

- 2. Open the hardware setup window ("Hardware Setup" button), select the JTAG cable you are using, and close the hardware setup window.

- 3. Select JTAG as "Mode"

- 4. Load the ".jic" file

- 5. Select configure (for both FPGA and EPCS devices)

- 6. Click the "Start" button

- 7. You can also verify and erase the EPCS if you want

For more information, check http://www.altera.com/literature/an/an370.pdf

## 25 Graphic LCD

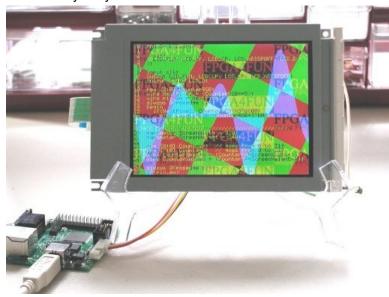

## 25.1 KNJN graphic LCDs (all boards)

KNJN graphic LCDs connect to the secondary connector of your board (see 11.6), using an adapter module (provided with the LCD) that makes the connection very easy.

These LCDs use a video-like interface and so are well adapted to be driven from an FPGA. See <a href="here">here</a> for the list of available LCDs and <a href="here">here</a> for an example of use.

Some LCDs and FPGA boards can be used with a Flashy board to create an oscilloscope with external display. See FlashyDemo in chapter 27.2 for more information.

## 25.2 LVDS LCD panel (Dragon-E only)

Dragon-E features a special LCD connector to connect an LVDS TFT 1024x600 color LCD panel with CCFL backlight. The LCD is available as a Dragon-E purchase option and it comes with the matching FFC cable.

The LVDS LCD requires both 3.3V and 5V powers – see chapter 32 for power options.

## 25.3 Other graphic LCDs

Other LCDs can be used. Please note that they may require a special connector, many IOs and non-standard voltages.

# 26 Flashy

### 26.1 What is Flashy

<u>Flashy</u> is a high-speed acquisition board. When used in conjunction with a KNJN FPGA board, the system becomes a digital oscilloscope.

The FPGA boards include two Flashy designs:

- 1. The FlashyMini design (27.1) comes with HDL and C source codes.

- 2. The Flashy demo design (chapter 27) comes with a GUI to use Flashy as an oscilloscope.

### 26.2 Flashy connection

Before using Flashy, you have to connect it to your FPGA board.

Proceed as follow:

- 1. Make sure the FPGA board is NOT powered (unplug it from USB).

- 2. Plug Flashy/FlashyD into the FPGA board.

For example with Saxo:

Now you are ready to run FlashyMini or FlashyDemo (next chapter).

## 27 Flashy designs

Two Flashy designs are provided in the startup kit: FlashyMini and FlashyDemo.

### 27.1 FlashyMini

FlashyMini is a simple design that displays the acquired data in text form. FlashyMini is provided with source code and can be used as a skeleton to develop your own acquisition project.

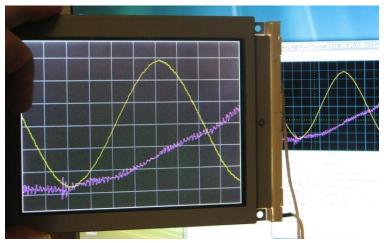

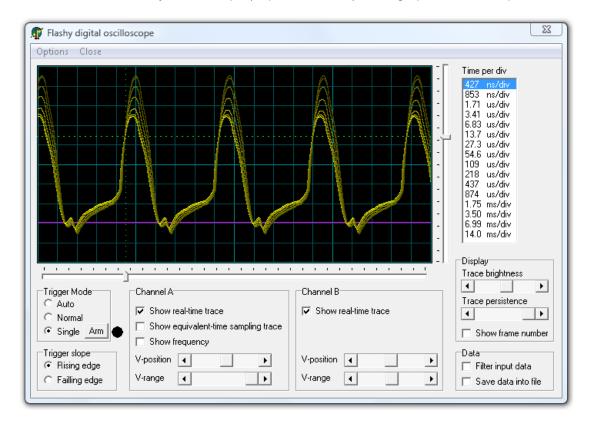

#### 27.2 FlashyDemo

FlashyDemo is a showcase of Flashy possibilities, implementing features found in regular oscilloscopes, like pretriggering and equivalent-time-sampling.

To run FlashyDemo:

- Open FPGAconf and configure the FPGA with the FlashyDemo bitfile (find it in the FPGA Project FlashyDemo directory).

- Go to Menu → Tools → Flashy Oscilloscope (or press CTRL-F) to bring-up the oscilloscope window.